# User Manual

CSM-B79

Carrier Board for SMARC<sup>®</sup> Rel. 2.0 / 2.1 compliant modules

# www.seco.com

### **REVISION HISTORY**

| Revision | Date                            | Note                                                | Rif |

|----------|---------------------------------|-----------------------------------------------------|-----|

| 1.0      | 30 <sup>th</sup> August 2021    | First official release                              | AR  |

| 1.1      | 22 <sup>nd</sup> September 2021 | Updated SMARC MXM Connector on pins S78-S79-S81-S82 | AR  |

|          |                                 |                                                     |     |

|          |                                 |                                                     |     |

All rights reserved. All information contained in this manual is proprietary and confidential material of SECO S.p.A.

Unauthorised use, duplication, or modification by any means without prior consent of SECO S.p.A. is prohibited.

Every effort has been made to ensure the accuracy of this manual. However, SECO S.p.A. accepts no responsibility for any inaccuracies, errors or omissions herein. SECO S.p.A. reserves the right to change precise specifications without prior notice to supply the best product possible.

For further information on this module or other SECO products, but also to get the required assistance for any and possible issues, please contact us using the dedicated web form available at <u>http://www.seco.com</u> (registration required).

Our team is ready to assist.

## INDEX

| Chapter      | 1. INTRODUCTION             | . 5  |

|--------------|-----------------------------|------|

| 1.1          | Warranty                    | 6    |

| 1.2          | Information and assistance  | 7    |

| 1.3          | RMA number request          | 7    |

| 1.4          | Safety                      | 8    |

| 1.5          | Electrostatic Discharges    | 8    |

| 1.6          | RoHS compliance             | 8    |

| 1.7          | Safety Policy               | 9    |

| 1.8          | Terminology and definitions | . 10 |

| 1.9          | Reference specifications    | .13  |

| Chapter      | 2. OVERVIEW                 | 15   |

| 2.1          | Introduction                | .16  |

| 2.2          | Technical Specifications    | .17  |

| 2.3          | Electrical Specifications   | .18  |

| 2.3.         | 1 Smart Battery Connector   | .18  |

| 2.3.         |                             |      |

| 2.3.         |                             |      |

| 2.3.         | 5                           |      |

| 2.4          | Mechanical Specifications   |      |

| 2.5          | Block Diagram.              |      |

| Chapter      |                             |      |

| 3.1          | Connectors placement        |      |

| 3.2          | Connectors overview         |      |

| 3.2.         |                             |      |

| 3.2.         |                             |      |

| 3.3          | Connectors description      |      |

| 3.3.         |                             |      |

| 3.3.<br>3.3. |                             |      |

| 3.3.         |                             |      |

| 0.0.         |                             |      |

| 3.3.5     | 5 HDMI / DP1++ connectors       |    |

|-----------|---------------------------------|----|

| 3.3.6     | 5 DP0++ connector               |    |

| 3.3.7     | 7 CSI Camera Connector          |    |

| 3.3.8     | 3 S-ATA connectors              |    |

| 3.3.9     | 9 S-ATA Power Connector         |    |

| 3.3.1     | 10 microSD Slot                 |    |

| 3.3.1     | 11 Gigabit Ethernet connectors  |    |

| 3.3.1     | 12 M.2 WLAN Key E Slot          | 51 |

| 3.3.1     | 13 M.2 WWAN Key B Slot          | 53 |

| 3.3.1     | I 4 microSIM Slot               |    |

| 3.3.1     | 15 PCI-e ports                  |    |

| 3.3.1     | 16 USB Connectors               |    |

| 3.3.1     | 17 Audio Connectors             | 62 |

| 3.3.1     | 18 COM Port Header              | 64 |

| 3.3.1     | 19 CAN ports                    |    |

| 3.3.2     | 20 USB Debug Connector          |    |

| 3.3.2     | 21 FAN Connector                | 67 |

| 3.3.2     | 22 SPI interface                | 67 |

| 3.3.2     | 23 eSPI interface               |    |

| 3.3.2     | 24 I2C EEPROM Socket            |    |

| 3.3.2     | 25 JTAG Connector               |    |

| 3.3.2     | 26 Feature Header               |    |

| 3.3.2     | 27 GPIO / FuSa Header           | 72 |

| 3.3.2     | 28 Boot Select switches         | 73 |

| 3.3.2     | 29 POST Code Display            | 73 |

| 3.3.3     | 30 Buttons                      | 74 |

| 3.3.3     | 31 Others configuration Jumpers | 74 |

| 3.3.3     | 32 Power / Status LEDs          |    |

| Chapter 4 | 4. Appendices                   | 76 |

| 4.1       | Thermal Design                  | 77 |

| 4.2 A     | Accessories                     |    |

|           |                                 |    |

# Chapter 1. INTRODUCTION

- Warranty

- Information and assistance

- RMA number request

- Safety

- Electrostatic Discharges

- RoHS compliance

- Safety Policy

- Terminology and definitions

- Reference specifications

## 1.1 Warranty

This product is subject to the Italian Law Decree 24/2002, acting European Directive 1999/44/CE on matters of sale and warranties to consumers. The warranty on this product lasts for 1 year.

Under the warranty period, the Supplier guarantees the buyer assistance and service for repairing, replacing or credit of the item, at the Supplier's own discretion.

Shipping costs that apply to non-conforming items or items that need replacement are to be paid by the customer.

Items cannot be returned unless previously authorised by the supplier.

The authorisation is released after completing the specific form available on the web-site <u>https://www.seco.com/us/support/online-rma.html</u> (RMA Online). The RMA authorisation number must be put both on the packaging and on the documents shipped with the items, which must include all the accessories in their original packaging, with no signs of damage to, or tampering with, any returned item.

The error analysis form identifying the fault type must be completed by the customer and has must accompany the returned item.

If any of the above-mentioned requirements for RMA is not satisfied, the item will be shipped back and the customer will have to pay any and all shipping costs.

Following a technical analysis, the supplier will verify if all the requirements, for which a warranty service applies, are met. If the warranty cannot be applied, the Supplier will calculate the minimum cost of this initial analysis on the item and the repair costs. Costs for replaced components will be calculated separately.

Warning! All changes or modifications to the equipment not explicitly approved by SECO S.p.A. could impair the equipment's functionality and could void the warranty

#### 1.2 Information and assistance

What do I have to do if the product is faulty?

SECO S.p.A. offers the following services:

- SECO website: visit <u>http://www.seco.com</u> to receive the latest information on the product. In most of the cases it is possible to find useful information to solve the problem.

- SECO Sales Representative: the Sales Rep can help to determine the exact cause of the problem and search for the best solution.

- SECO Help-Desk: contact SECO Technical Assistance. A technician is at disposal to understand the exact origin of the problem and suggest the correct solution.

E-mail: technical.service@seco.com

Fax (+39) 0575 350210

- Repair center: it is possible to send the faulty product to the SECO Repair Centre. In this case, follow this procedure:

- o Returned items must be accompanied by a RMA Number. Items sent without the RMA number will be not accepted.

- Returned items must be shipped in an appropriate package. SECO is not responsible for damages caused by accidental drop, improper usage, or customer neglect.

Note: Please have the following information before asking for technical assistance:

- Name and serial number of the product;

- Description of Customer's peripheral connections;

- Description of Customer's software (operating system, version, application software, etc.);

- A complete description of the problem;

- The exact words of every kind of error message encountered.

## 1.3 RMA number request

To request an RMA number, please visit SECO's web-site. On the home page, please select "RMA Online" and follow the procedure described. An RMA Number will be sent within 1 working day (only for on-line RMA requests).

## 1.4 Safety

The CSM-B79 board uses only extremely low voltages.

While handling the board, please use extreme caution to avoid any kind of risk or damages to electronic components.

Always switch the power off, and unplug the power supply unit, before handling the board and/or connecting cables or other boards.

Avoid using metallic components - like paper clips, screws and similar - near the board when connected to a power supply, to avoid short circuits due to unwanted contacts with other board components.

If the board has become wet, never connect it to any external power supply unit or battery.

Check carefully that all cables are correctly connected and that they are not damaged.

#### 1.5 Electrostatic Discharges

The CSM-B79 board, like any other electronic product, is an electrostatic sensitive device: high voltages caused by static electricity could damage some or all the devices and/or components on-board.

Whenever handling a CSM-B79 board, ground yourself through an anti-static wrist strap. Placement of the board on an anti-static surface is also highly recommended.

#### 1.6 RoHS compliance

The CSM-B79 board is designed using RoHS compliant components and is manufactured on a lead-free production line. It is therefore fully RoHS compliant.

# 1.7 Safety Policy

In order to meet the safety requirements of EN62368-1:2014 standard for Audio/Video, information and communication technology equipment, the CSM-B79 Carrier Board shall be:

- used inside a fire enclosure made of non-combustible material or V-1 material (the fire enclosure is not necessary if the maximum power supplied to the board never exceeds 100 W, even in worst-case fault);

- used inside an enclosure provided with the symbol IEC 60417-5041 (element 1a according to clause 9.5.2 of the IEC 62368-1) on the external part;

- installed inside an enclosure compliant with all applicable IEC 62368-1 requirements;

The manufacturer which includes a CSM-B79 Carrier Board in his end-user product shall:

- verify the compliance with B.2 and B.3 clauses of the EN62368-1 standard when the module works in its own final operating condition

- prescribe temperature and humidity range for operating, transport and storage conditions;

- prescribe to perform maintenance on the board only when it is off and has already cooled down;

- prescribe that the connections from or to the board have to be compliant to ES1 requirements;

- the board in its enclosure must be evaluated for temperature and airflow considerations.

# 1.8 Terminology and definitions

| ACPI       | Advanced Configuration and Power Interface, an open industrial standard for the board's devices configuration and power management                                         |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AHCI       | Advanced Host Controller Interface, a standard which defines the operation modes of SATA interface                                                                         |

| API        | Application Program Interface, a set of commands and functions that can be used by programmers for writing software for specific Operating Systems                         |

| AVC        | Advanced Video Coding, a video compression standard, also known as H.264                                                                                                   |

| BIOS       | Basic Input / Output System, the Firmware Interface that initializes the board before the OS starts loading                                                                |

| CAN Bus    | Controller Area network, a protocol designed for in-vehicle communication                                                                                                  |

| DDC        | Display Data Channel, a kind of I2C interface for digital communication between displays and graphics processing units (GPU)                                               |

| DDR        | Double Data Rate, a typology of memory devices which transfer data both on the rising and on the falling edge of the clock.                                                |

| DP         | Display Port, a type of digital video display interface                                                                                                                    |

| eDP        | embedded Display Port, a type of digital video display interface developed especially for internal connections between boards and digital displays                         |

| GBE        | Gigabit Ethernet                                                                                                                                                           |

| Gbps       | Gigabits per second                                                                                                                                                        |

| GND        | Ground                                                                                                                                                                     |

| GPI/O      | General purpose Input/Output                                                                                                                                               |

| HEVC       | High Efficiency Video Coding, a video compression standard, also known as H.265                                                                                            |

| HD Audio   | High Definition Audio, most recent standard for hardware codecs developed by Intel® in 2004 for higher audio quality                                                       |

| HDMI       | High Definition Multimedia Interface, a digital audio and video interface                                                                                                  |

| I2C Bus    | Inter-Integrated Circuit Bus, a simple serial bus consisting only of data and clock line, with multi-master capability                                                     |

| I2S        | Inter-Integrated Circuit Sound, an audio serial bus protocol interface developed by Philips (now NXP) in 1986                                                              |

| JPEG/MJPEG | Joint Photographic Experts Group, standard method for lossy compression of digital images. Motion JPEG is a video compression format                                       |

| LAN        | Local Area Network                                                                                                                                                         |

| LPDDR4     | Low-Power Double Data Rate Synchronous Dynamic Random Access Memory, 4th generation                                                                                        |

| LVDS       | Low Voltage Differential Signalling, a standard for transferring data at very high speed using inexpensive twisted pair copper cables, usually used for video applications |

| Mbps       | Megabits per second                                                                                                                                                        |

| MIPI       | Mobile Industry Processor Interface alliance                                                                                                                               |

| MMC/eMMC   | MultiMedia Card / embedded MMC, a type of memory card, having the same interface as the SD card. The eMMC is the embedded version of                                       |

|            |                                                                                                                                                                            |

| MPEG2<br>MVC<br>N.A.<br>N.C.<br>OpenCL<br>OpenGL<br>OpenVG<br>OS<br>PCI-e<br>PHY<br>PWM<br>PWR | the MMC. They are devices that incorporate the flash memories on a single BGA chip.<br>Standard for the generic coding of moving pictures and associated audio information<br>Multiview Video Coding, a stereoscopic video coding standard for video compression<br>Not Applicable<br>Not Connected<br>Open Computing Language, specifies programming languages for programming different devices and API<br>Open Graphics Library, an Open Source API dedicated to 2D and 3D graphics<br>Open Vector Graphics, an Open Source API dedicated to hardware accelerated 2D vector graphics<br>Operating System<br>Peripheral Component Interface Express<br>Abbreviation of Physical, it is the device implementing the Physical Layer of ISO/OSI-7 model for communication systems<br>Pulse Width Modulation<br>Power |

|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RGMI                                                                                           | Reduced Gigabit Media Independent Interface, a standard interface between the Ethernet Media Access Control (MAC) and the Physical Layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| (PHY)<br>SATA                                                                                  | Social Advance Technology Attachment a differential full duplay social interface for Llard Dicks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SD                                                                                             | Serial Advance Technology Attachment, a differential full duplex serial interface for Hard Disks<br>Secure Digital, a memory card type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SDIO                                                                                           | Secure Digital Input/Output, an evolution of the SD standard that allows the use of the same SD interface to drive different Input/Output devices,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                | like cameras, GPS, Tuners and so on.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SGET                                                                                           | Standardization Group for Embedded Technologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SMARC                                                                                          | Smart Mobility Architecture, a computer Module standard maintained by the SGET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SM Bus                                                                                         | System Management Bus, a subset of the I2C bus dedicated to communication with devices for system management, like a smart battery and other power supply-related devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SOC                                                                                            | System-on-a-chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SPI                                                                                            | Serial Peripheral Interface, a 4-Wire synchronous full-duplex serial interface which is composed of a master and one or more slaves, individually<br>enabled through a Chip Select line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TBM                                                                                            | To be measured                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TMDS                                                                                           | Transition-Minimized Differential Signalling, a method for transmitting high speed serial data, normally used on DVI and HDMI interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| UART                                                                                           | Universal Asynchronous Receiver-Transmitter, is an asynchronous serial interface where data format and transmission speed are configurable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| UEFI                                                                                           | Unified Extensible Firmware Interface, a specification defining the interface between the OS and the board's firmware. It is meant to replace the original BIOS interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

- USB Universal Serial Bus

- VP8 Open video compression format, a traditional block-based transform coding format

- VP9 Successor to VP8, customized for video greater than 1080p

- WMV9 Series 9 of Windows Media Video, a video compression format inlcuding native support for interlaced video, non-square pixels, and frame interpolation

# 1.9 Reference specifications

Here below it is a list of applicable industry specifications and reference documents.

| Reference                          | Link                                                                                                                       |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| ACPI                               | https://uefi.org/specifications                                                                                            |

| AHCI                               | http://www.intel.com/content/www/us/en/io/serial-ata/ahci.html                                                             |

| CAN Bus                            | http://www.bosch-semiconductors.de/en/ubk_semiconductors/safe/ip_modules/can_literature/can_literature.html                |

| DDC                                | http://www.vesa.org                                                                                                        |

| DP, eDP                            | http://www.vesa.org                                                                                                        |

| FastEthernet                       | http://standards.ieee.org/about/get/802/802.3.html                                                                         |

| Gigabit Ethernet                   | https://standards.ieee.org/standard/802_3-2018.html                                                                        |

| HD Audio                           | http://www.intel.com/content/dam/www/public/us/en/documents/product-specifications/high-definition-audio-specification.pdf |

| HDMI                               | http://www.hdmi.org/index.aspx                                                                                             |

| I2C                                | http://www.nxp.com/documents/other/UM10204_v5.pdf                                                                          |

| I2S                                | https://www.sparkfun.com/datasheets/BreakoutBoards/I2SBUS.pdf                                                              |

| LVDS                               | http://www.ti.com/ww/en/analog/interface/lvds.shtml and http://www.ti.com/lit/ml/snla187/snla187.pdf                       |

| MIPI                               | http://www.mipi.org                                                                                                        |

| MMC/eMMC                           | http://www.jedec.org/committees/jc-649                                                                                     |

| PCI Express                        | http://www.pcisig.com/specifications/pciexpress                                                                            |

| SATA                               | https://www.sata-io.org                                                                                                    |

| SMARC Design Guide 2.1             | SMARC Design Guide 2.1.1 (sget.org)                                                                                        |

| SMARC Hardware Specification 2.1.1 | https://sget.org/wp-content/uploads/2020/05/SMARC_V211.pdf                                                                 |

| SD Card Association                | https://www.sdcard.org/home                                                                                                |

| SDIO                               | https://www.sdcard.org/developers/overview/sdio                                                                            |

| SM Bus                             | http://www.smbus.org/specs                                                                                                 |

| TMDS                               | http://www.siliconimage.com/technologies/tmds                                                                              |

| UEFI                | http://www.uefi.org                                                                  |

|---------------------|--------------------------------------------------------------------------------------|

| USB 2.0 and USB OTG | http://www.usb.org/developers/docs/usb_20_070113.zip                                 |

| USB 3.0             | https://usb.org.10-1-108-210.causewaynow.com/sites/default/files/usb_32_20191024.zip |

# Chapter 2. OVERVIEW

- Introduction

- Technical Specifications

- Electrical Specifications

- Mechanical Specifications

- Block Diagram

## 2.1 Introduction

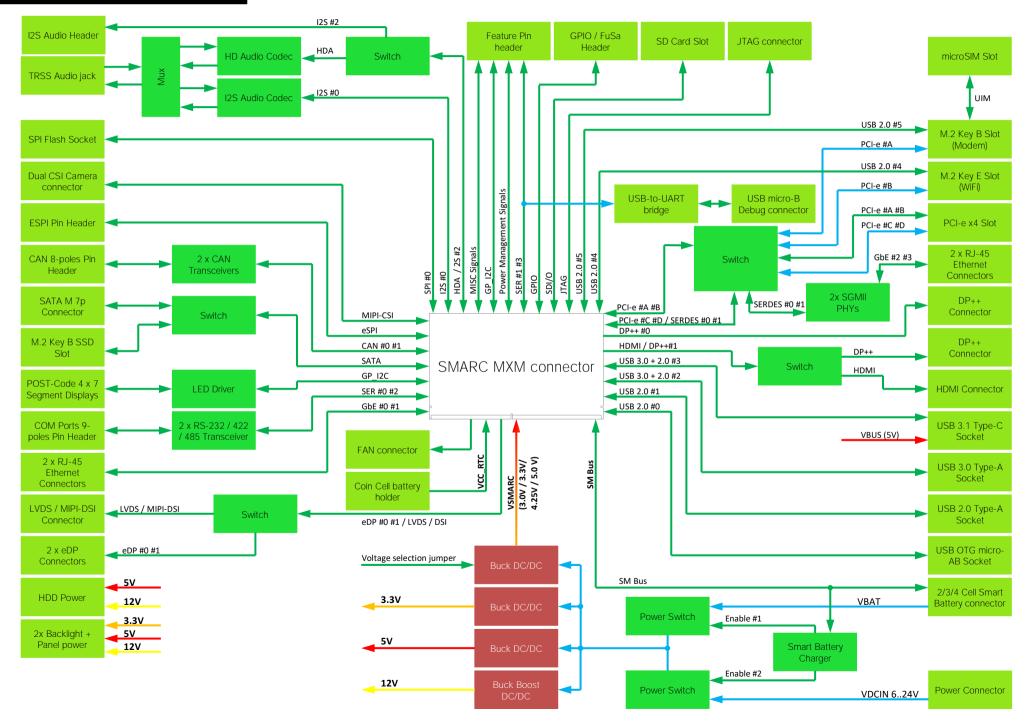

The CSM-B79 is a carrier board for SMARC<sup>®</sup> Rel. 2.0 / 2.1 compliant modules, designed in microATX form factor.

SMARC ("Smart Mobility Architecture") is a computer Module standard maintained by the SGET consortium.

SMARC<sup>®</sup> Modules are small form factor (82mm x 50mm), low power computer Modules that integrates all core components of a common PC architecture (CPU, RAM, Graphic, audio, etc.). All the functionalities are made available through a standardized card edge connector, from which all signals can be taken and carried to the appropriate external connector in the carrier board and/or to other internal component, to implement more functionalities other than included in the standard SMARC<sup>®</sup> bus interface.

SMARC<sup>®</sup> Modules are used on a Carrier board that utilizes a 314 pin 0.5mm pitch right-angle memory socket style connector to host the Module.

SMARC® Modules may utilize ARM, low power RISC or low power x86 CPUs / SOCs.

The list of features that are effectively available depends on the configuration of the SMARC<sup>®</sup> module used.

CSM-B79 carrier board is specially designed for being both an advanced development board, for skilled users who want to design their own carrier boards, and a good solution for mass production, for customers whose needing are satisfied by this compact and versatile Carrier Board.

All the components mounted onboard are certified for industrial temperature range.

Please refer to following chapter for a complete list of all peripherals integrated and characteristics.

### 2.2 Technical Specifications

Supported Modules SMARC<sup>®</sup> Rel. 2.0 / 2.1 compliant modules Video interfaces LVDS/MIPI-DSI connector, interface shared with 2x eDP connectors Backlight control + LCD selectable voltages dedicated connector 2x DP++ connectors HDMI connector (can be used in alternative to 1x DP++) 2x CSI Camera input interfaces Mass Storage interfaces 1x SATA 7p M connector with dedicated power connector, interface shared with M.2 Socket 2 2230 / 2242 / 2260 Key B SSD slot **u**SD Card slot Networking 2x Dual RJ-45 Gigabit Ethernet connector M.2 Socket1 2230 Key E Slot for WiFi/BT Modules (interface shared with PCI-e x4 slot)

M.2 Socket 2 2260 / 3042 Key B Slot for WWAN Modem Modules (interface shared with PCI-e x 4 slot), connected to on-board microSIM slot

#### USB

1 x USB 3.0 type A Socket

1 x USB 2.0 type A Socket

1 x USB OTG micro-AB Socket

1 x USB 3.1 Type-C Socket

#### PCI-e

PCI-e x4 slot, interface shared with M.2 Slots

CSM-B79

#### Audio

TRSS Audio Jack

Onboard I2S Audio Codec (TI TLV320AIC3204) + HD Audio Codec (Cirrus Logic CS4207)

I2S Audio header

#### Serial Ports

2 x CAN ports

2 x RS-232/RS-422/RS-485 configurable serial ports on internal pin header

2 x Serial ports (Tx/Rx signals only, TTL level) on feature header

#### Other Interfaces

eSPI pin header + Flash Socket

- SPI pin header + Flash Socket

- I2C EEPROM Socket

- 4 x 7-segment LCD displays for POST codes

Feature pin header with 2 x Serial ports, I2C, SM Bus, Watchdog

and Power Management Signals

GPIO / FuSa header

FAN connector

Optional Debug USB port on micro-B connector

Boot selection switches

JTAG connector

Selector for SMARC® 2.0 / 2.1 pinout compatibility

Power supply:

- $9 \div 24V_{\text{DC}}$  through dedicated Mini-Fit Jr 2x2 power connector

- 6 ÷ 17V<sub>DC</sub> through 2/3/4 Cell Smart Battery Connector

RTC Coin cell battery holder

Operating temperature: -40°C ÷ +85°C \*

Dimensions: 243.84 x 243.84mm (microATX)

\* Temperature ranges indicated mean that all components available onboard are certified for working with a Tcase included in these temperature ranges. This means that it is customer's responsibility to ensure that all components' Tcases remain in the range above indicated. Please also check paragraph 4.1.

### 2.3 Electrical Specifications

CSM-B79 board needs to be supplied with a single voltage in the range  $9V_{DC}$ .. +  $24V_{DC}$ . All the others voltages necessary for the working of the board and of the connected peripherals are derived from the main  $V_{IN}$  power rail.

|    |   |        | Power IN Connect | or | – CN3  |  |

|----|---|--------|------------------|----|--------|--|

| Pi | n | Signal | Pin              | S  | Signal |  |

| -  | 1 | GND    | 2                | C  | GND    |  |

| 3  | 3 | VIN    | 4                | V  | /IN    |  |

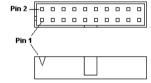

The power connector is type Molex Mini-Fit Jr connector, type MOLEX p/n 39-28-1043 or equivalent.

The pin-out is indicated in the table here on the left, and the mating connector is MOLEX p/n 39-01-2040 or equivalent with crimp terminals series 5556/44476.

| in 3 | Pin 4 |

|------|-------|

|      |       |

|      |       |

ৰ্ব্যাৰ্ব্যাৰ্থনি

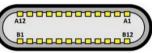

#### 2.3.1 Smart Battery Connector

It is possible to supply the board also by using external SMART batteries. Input voltage range, in this case, must be in the range 6..17V<sub>DC</sub>.

| SMART Battery Connector – CN6 |             | To do this, a 8-pin male connector is provided, type HR p/n A2001WR-S-08PD01 or equivalent, with pinout shown in the table on the left.                                                                                           |

|-------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin                           | Signal      | Mating connector: JST PHR-8 crimp housing with JST SPH-002T-P0.5L crimp terminals.                                                                                                                                                |

| 1                             | VBAT        | SMB_CLK_BAT: Smart Battery System Management bus bidirectional clock line, +3.3V_DSW electrical level with                                                                                                                        |

| 2                             | VBAT        | 2.2kΩ pull up resistor, derived by I2C_PM_CK signal                                                                                                                                                                               |

| 3                             | N.C.        | SMB_DAT_BAT: Smart Battery System Management bus bidirectional data line, +3.3V_DSW electrical level with $2.2k\Omega$                                                                                                            |

| 4                             | SMB_CLK_BAT | pull up resistor, derived by I2C_PM_DAT signal                                                                                                                                                                                    |

| 5                             | SMB_DAT_BAT | SAFETY: Smart Battery System Management safety input signal, used to communicate critical errors and/or safety mechanisms to prevent over-charging, over-discharging, over-temperature and other conditions that are dangerous or |

| 6                             | SAFETY      | could adversely affect battery longevity. This signal goes directly from the battery to the on-board charger.                                                                                                                     |

| 7                             | GND         |                                                                                                                                                                                                                                   |

| 8                             | GND         |                                                                                                                                                                                                                                   |

#### 2.3.2 RTC Battery

For the occurrences when the System (Carrier board + SMARC<sup>®</sup> module) is not powered with an external power supply, on board there is a RTC Coin Cell Battery holder CN2, for the use of standard coin battery type CR2032 with a nominal capacity of 220mAh, to supply, with a 3V voltage, the Real Time Clock and CMOS memory mounted on the SMARC<sup>®</sup> module.

The batteries should only be replaced with devices of the same type. Always check the orientation before inserting and make sure that they are aligned correctly and are not damaged or leaking.

#### CAUTION: handling batteries incorrectly or replacing with not-approved devices may present a risk of fire or explosion.

Never allow the batteries to become short-circuited during handling.

Batteries supplied with CSM-B79 board are compliant to requirements of European Directive 2006/66/EC regarding batteries and accumulators. When putting out of order CSM-B79 board, remove the batteries from the board in order to collect and dispose them according to the requirement of the same European Directive above mentioned. Even when replacing the batteries, the disposal has to be made according to these requirements.

| CN93 position | RTC Battery enable   |

|---------------|----------------------|

| 1-2           | Battery connected    |

| 2-3           | Battery disconnected |

| NO jumper     | Current measurement  |

It is possible to monitor the consumption on VDD\_RTC battery by removing the jumper from CN93 connector and inserting a tester in series set as ammeter between 1-2 position.

RTC battery can be enabled/disabled using dedicated jumper on CN93, which is a standard pin header, P2.54mm, 1x3 pin.

#### 2.3.3 SMARC Module's Power In Voltage selector

| CN8 position | VDD_IN SMARC Voltage |

|--------------|----------------------|

| 1-2          | 3.0V                 |

| 3-4          | 3.3V                 |

| 5-6          | 4.25V                |

| 7-8          | 5V                   |

According to SMARC<sup>®</sup> 2.1.1 specifications, SMARC<sup>®</sup> modules allow a power input voltage range of 3.0V to 5.25V for VDD\_IN.

Since the modules could be designed to work only with a fixed voltage value in this range, on CSM-B79 carrier board is possible to select module's power in voltage value by placing a jumper on CN8 header, type ADIMPEX p/n LE008208-R.

| 2 | • | $\bigcirc$ |   | •  | 8 |

|---|---|------------|---|----|---|

| 1 | Ŀ | ۰          | ۰ | ّ● | 7 |

#### 2.3.4 Power Rails meanings

In all the tables contained in this manual, Power rails are named with the following meaning:

VDD\_IN: SMARC<sup>®</sup> module power input voltage. Derived directly from VIN coming from Power IN Connector CN3. VDD\_IN value can be set by SMARC Module's Power In Voltage selector CN8 (par.2.3.3)

VDD\_RTC: Low current RTC circuit backup power. 3V coin cell voltage coming from the RTC Coin Cell Battery holder CN2 for supplying the RTC clock on SMARC<sup>®</sup> module.

\_RUN: Switched voltages, i.e. power rails that are active only when the board is in ACPI s S0 (Working) state. Examples:+3.3V\_RUN, +5V\_RUN.

\_ALW: Always-on voltages, i.e. power rails that are active both in ACPI s S0 (Working), S3 (Standby) and S5 (Soft Off) state. Examples: +5V\_ALW, +3.3V\_ALW.

\_DSW: Deep Sleep Well voltages, i.e. power rails that are derived directly from VIN coming from Power IN Connector CN3. Examples: +3.3V\_DSW, +1.8V\_DSW.

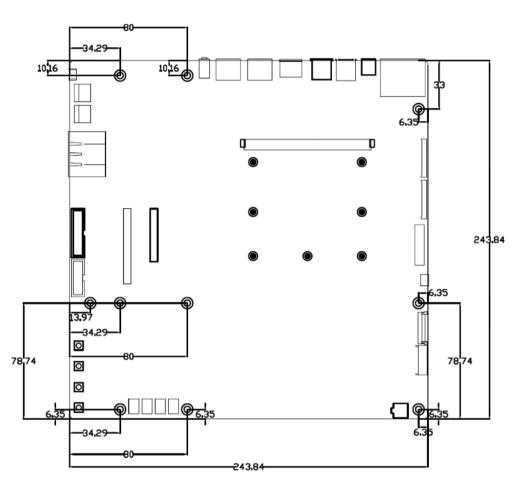

## 2.4 Mechanical Specifications

According to microATX form factor, board dimensions are 243.84 x 243.84 mm.

The printed circuit of the board is made of twelve layers, some of them are ground planes, for disturbance rejection.

In order to fix the SMARC<sup>®</sup> module to the carrier board, on CSM-B79 have been soldered seven metallic spacers, height 8mm, 2.5mm diameter module.

## 2.5 Block Diagram

# Chapter 3. CONNECTORS

- Connectors placement

- Connectors overview

- Connectors description

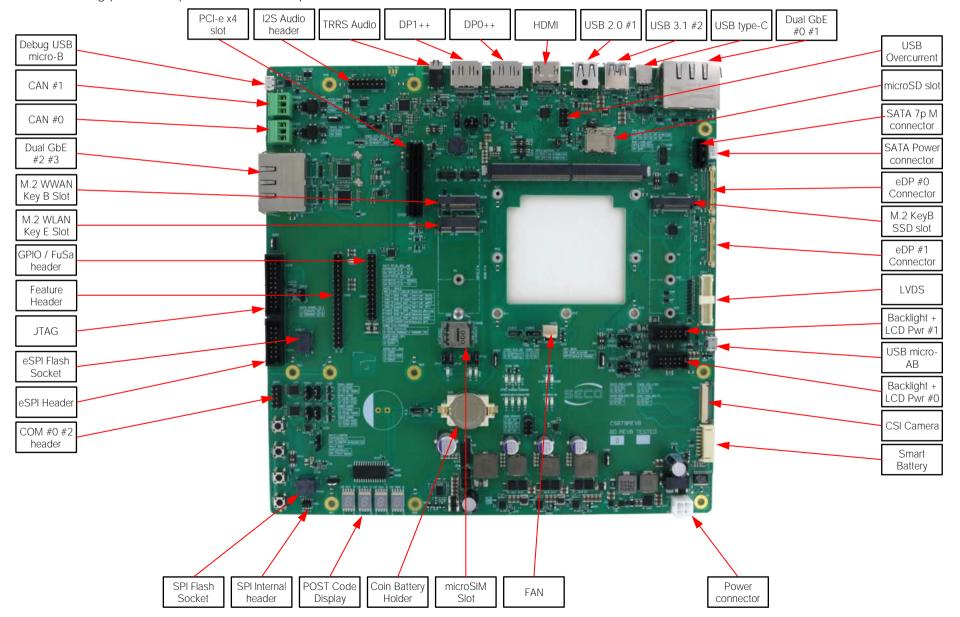

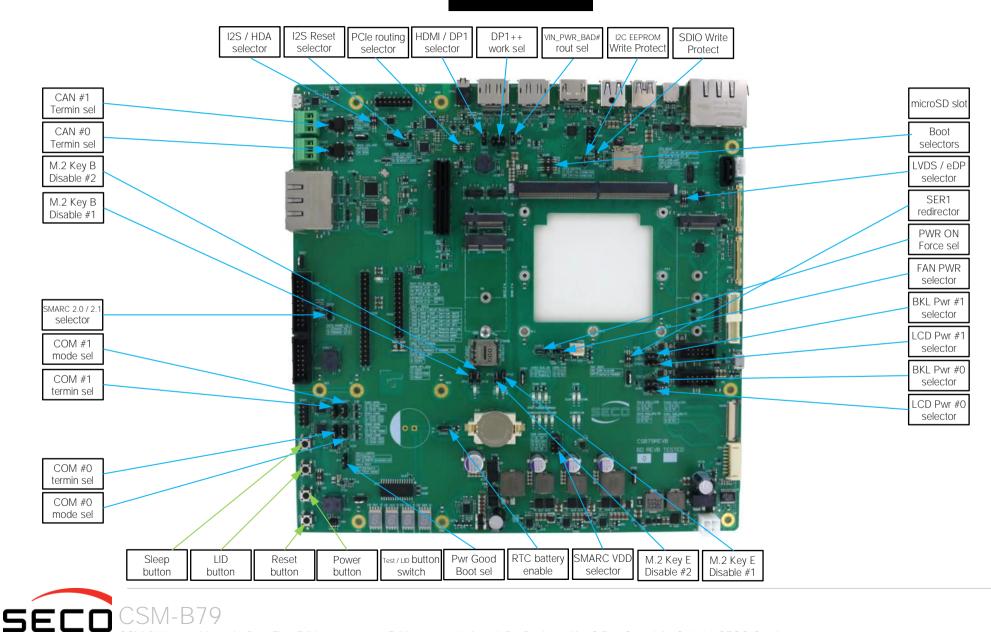

## 3.1 Connectors placement

On CSM-B79 carrier board, there are several connectors. Some of them are standard connectors, like Gigabit Ethernet, USB ports, and are placed on the same side of the board, so that they can be placed on a panel of a possible enclosure.

In the following picture it is possible to see the position of each connector.

JUMPER POSITION

### 3.2 Connectors overview

#### 3.2.1 Connectors list

| Name | Description                                 | Name | Description               |

|------|---------------------------------------------|------|---------------------------|

| CN2  | RTC Coin Cell Battery holder                | CN49 | SMARC MXM Connector       |

| CN3  | Power Connector                             | CN50 | USB 2.0 #1 Type-A Slot    |

| CN6  | Smart Battery Connector                     | CN56 | FAN Connector             |

| CN9  | USB 3.1 Type-C Socket                       | CN60 | eDP #0 Connector          |

| CN11 | DP1++ Connector                             | CN61 | eDP #1 Connector          |

| CN14 | LVDS / MIPI-DSI Connector                   | CN65 | CAN #0 PCB Terminal Block |

| CN16 | LCD Panel #0 Voltage connector              | CN66 | CAN #1 PCB terminal Block |

| CN17 | LCD Panel #1 Voltage connector              | CN69 | eSPI Flash Socket         |

| CN25 | COM #0 #2 internal Header                   | CN70 | JTAG Connector            |

| CN27 | Dual Gigabit Ethernet Connector (GbE #0 #1) | CN71 | I2C EEPROM Socket         |

| CN28 | Dual Gigabit Ethernet Connector (GbE #2 #3) | CN72 | USB 3.1 #2 type- A socket |

| CN30 | Micro-AB USB Connector                      | CN73 | Debug USB micro-B         |

| CN33 | PCI-e x4 slot                               | CN74 | DP0++ Connector           |

| CN34 | SATA 7p M Connector                         | CN77 | microSD Slot              |

| CN35 | M.2 Key B SSD Slot                          | CN79 | HDMI Connector            |

| CN36 | M.2 WLAN Key E Slot                         | CN80 | USB Overcurrent Header    |

| CN37 | S-ATA Power Connector                       | CN81 | I2S Audio Header          |

| CN38 | M.2 WWAN Key B Slot                         | CN91 | SPI Internal Header       |

| CN39 | CSI Camera Connector                        | CN92 | GPIO / FuSa Header        |

| CN40 | microSIM Slot                               |      |                           |

| CN41 | TRRS Audio jack                             |      |                           |

| CN43 | SPI Flash Socket                            |      |                           |

| CN44 | eSPI Header                                 |      |                           |

| CN45 | Feature Header                              |      |                           |

#### 3.2.2 Jumpers and switch list

| Name | Description                   | Name        | Description                         |

|------|-------------------------------|-------------|-------------------------------------|

| CN8  | SMARC VDD_IN Voltage selector | JP5         | SDIO Write Protect                  |

| CN18 | LCD #0 Power Selector         | JP12        | CAN #0 termination selector         |

| CN19 | BKLT #0 power selector        | JP13        | CAN #1 termination selector         |

| CN20 | LCD #1 Power Selector         | JP14        | I2C EEPROM Socket Write Protect     |

| CN21 | BKLT #1 power selector        | JP15        | M.2 Key E Wireless Disable #2       |

| CN23 | COM #0 mode selector          | JP16        | M.2 Key E Wireless Disable #1       |

| CN24 | COM #2 mode selector          | JP17        | M.2 Key B Wireless Disable #1       |

| CN53 | Power ON Force selector       | JP18        | M.2 Key B Wireless Disable #2       |

| CN55 | FAN Power Selector            | JP20        | Power Good controlled boot selector |

| CN62 | VIN_PWR_BAD# routing selector | SW3         | Power Button                        |

| CN63 | COM #0 Termination selector   | SW4         | Reset Button                        |

| CN64 | COM #2 Termination selector   | SW5         | Sleep Button                        |

| CN75 | HDMI / DP1++ selector         | SW6         | LVDS / eDP selector                 |

| CN76 | DP1++ Working mode selector   | SW7         | SER #1 routing selector             |

| CN78 | SMARC 2.0 / 2.1 selector      | SW12 / SW13 | BOOT Selectors                      |

| CN82 | I2S Reset selector            | SW14        | Test and Lid Button debug switch    |

| CN93 | RTC Battery enable            | SW15        | LID Button                          |

|      |                               | SW16        | I2S / HDA Codec selector            |

|      |                               | SW17        | PCIe routing selector               |

|      |                               |             |                                     |

# 3.3 Connectors description

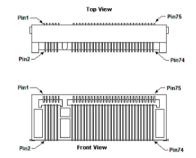

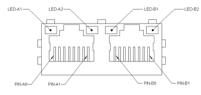

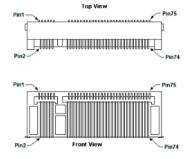

#### 3.3.1 SMARC Connector

According to SMARC Rel. 2.1.1 specification, all interface signals are reported on the card edge connector, which is a 314-pin Card Edge that can be inserted into standard low profile 314 pin 0.5mm right pitch angle connector that was originally defined for use with MXM3 graphics cards.

Not all signals contemplated in SMARC<sup>®</sup> standard are implemented on MXM3 connector, due to the functionalities really implemented on CSM-B79.

Therefore, please refer to the following table for a list of effective signals reported on MXM3 connector. Please be aware that on signals' description, Input and Output (if specifically written) are referred to the SMARC<sup>®</sup> module, i.e. they are inputs and outputs of the module itself, not of the carrier board (where they are, respectively, outputs and inputs).

| SMARC MXM Connector – CN49 |      |            |             |         |              |      |                         |  |  |  |

|----------------------------|------|------------|-------------|---------|--------------|------|-------------------------|--|--|--|

|                            | TO   | P SIDE     | BOTTOM SIDE |         |              |      |                         |  |  |  |

| SIGNAL GROUP               | Туре | Pin name   | Pin nr.     | Pin nr. | Pin name     | Туре | SIGNAL GROUP            |  |  |  |

|                            |      |            |             | S1      | I2C_CAM1_CK  | I/O  | CSI1 CAMERA INTERFACE   |  |  |  |

| MANAGEMENT                 | I    | SMB_ALERT# | P1          | S2      | I2C_CAM1_DAT | I/O  | CSI1 CAMERA INTERFACE   |  |  |  |

|                            |      | GND        | P2          | S3      | GND          |      |                         |  |  |  |

| CSI1 CAMERA INTERFACE      | I    | CSI1_CK+   | P3          | S4      | RSVD#S4      | I/O  | Reserved Purpose Signal |  |  |  |

| CSI1 CAMERA INTERFACE      | I    | CSI1_CK-   | P4          | S5      | I2C_CAM0_CK  | I/O  | CSIO CAMERA INTERFACE   |  |  |  |

| GBE                        | I/O  | GBE1_SDP   | P5          | S6      | CAM_MCK      | 0    | CSIO/1 CAMERA INTERFACE |  |  |  |

| GBE                        | I/O  | GBE0_SDP   | P6          | S7      | I2C_CAM0_DAT | I/O  | CSIO CAMERA INTERFACE   |  |  |  |

| CSI1 CAMERA INTERFACE      | I    | CSI1_RX0+  | P7          | S8      | CSIO_CK+     | I    | CSIO CAMERA INTERFACE   |  |  |  |

| CSI1 CAMERA INTERFACE      | I    | CSI1_RX0-  | P8          | S9      | CSIO_CK-     | I    | CSIO CAMERA INTERFACE   |  |  |  |

|                            |      | GND        | P9          | S10     | GND          |      |                         |  |  |  |

| CSI1 CAMERA INTERFACE      | I    | CSI1_RX1+  | P10         | S11     | CSIO_RXO+    | I.   | CSIO CAMERA INTERFACE   |  |  |  |

| CSI1 CAMERA INTERFACE      | I    | CSI1_RX1-  | P11         | S12     | CSIO_RXO-    | I    | CSIO CAMERA INTERFACE   |  |  |  |

|                            |      | GND        | P12         | S13     | GND          |      |                         |  |  |  |

| CSI1 CAMERA INTERFACE      |      | CSI1_RX2+  | P13         | S14     | CSIO_RX1+    | I    | CSIO CAMERA INTERFACE   |  |  |  |

| CSI1 CAMERA INTERFACE      | I    | CSI1_RX2-  | P14         | S15     | CSIO_RX1-    | I.   | CSIO CAMERA INTERFACE   |  |  |  |

|                            |      | GND        | P15         | S16     | GND          |      |                         |  |  |  |

|                       |     |                | -   |     |                           |     |                |

|-----------------------|-----|----------------|-----|-----|---------------------------|-----|----------------|

| CSI1 CAMERA INTERFACE |     | CSI1_RX3+      | P16 | S17 | GBE1_MDI0+                | I/O | GBE            |

| CSI1 CAMERA INTERFACE | I   | CSI1_RX3-      | P17 | S18 | GBE1_MDIO-                | I/O | GBE            |

|                       |     | GND            | P18 | S19 | GBE1_LINK100#             | 0   |                |

| GBE                   | I/O | GBE0_MDI3-     | P19 | S20 | GBE1_MDI1+                | I/O | GBE            |

| GBE                   | I/O | GBE0_MDI3+     | P20 | S21 | GBE1_MDI1-                | I/O | GBE            |

| GBE                   | 0   | GBE0_LINK100#  | P21 | S22 | GBE1_LINK1000#            | 0   |                |

| GBE                   | 0   | GBE0_LINK1000# | P22 | S23 | GBE1_MDI2+                | I/O | GBE            |

| GBE                   | I/O | GBE0_MDI2-     | P23 | S24 | GBE1_MDI2-                | I/O | GBE            |

| GBE                   | I/O | GBE0_MDI2+     | P24 | S25 | GND                       |     |                |

| GBE                   | 0   | GBE0_LINK_ACT# | P25 | S26 | GBE1_MDI3-                | I/O | GBE            |

| GBE                   | I/O | GBE0_MDI1-     | P26 | S27 | GBE1_MDI3+                | I/O | GBE            |

| GBE                   | I/O | GBE0_MDI1+     | P27 | S28 | GBE1_CTREF                | 0   | GBE            |

| GBE                   | 0   | GBE0_CTREF     | P28 | S29 | SERDES_0_TX+ / PCIE_D_TX+ | 0   | SERDES / PCI-e |

| GBE                   | I/O | GBE0_MDI0-     | P29 | S30 | SERDES_0_TX- / PCIE_D_TX- | 0   | SERDES / PCI-e |

| GBE                   | I/O | GBE0_MDI0+     | P30 | S31 | GBE1_LINK_ACT#            | 0   | GBE            |

| SPI 0 INTERFACE       | 0   | SPI0_CS1#      | P31 | S32 | SERDES_0_RX+ / PCIE_D_RX+ | I   | SERDES / PCI-e |

|                       |     | GND            | P32 | S33 | SERDES_0_RX- / PCIE_D_RX- | 1   | SERDES / PCI-e |

| SDIO_CARD             |     | SDIO_WP        | P33 | S34 | GND                       |     |                |

| SDIO_CARD             | I/O | SDIO_CMD       | P34 | S35 | USB4+                     | I/O | USB            |

| SDIO_CARD             |     | SDIO_CD#       | P35 | S36 | USB4-                     | I/O | USB            |

| SDIO_CARD             | 0   | SDIO_CK        | P36 | S37 | USB3_VBUS_DET             | I   | USB            |

| SDIO_CARD             | 0   | SDIO_PWR_EN    | P37 | S38 | AUDIO_MCK                 | 0   | AUDIO          |

|                       |     | GND            | P38 | S39 | I2S0_LRCK                 | I/O | AUDIO          |

| SDIO_CARD             | I/O | SDIO_DO        | P39 | S40 | I2S0_SDOUT                | 0   | AUDIO          |

| SDIO_CARD             | I/O | SDIO_D1        | P40 | S41 | I2S0_SDIN                 | 1   | AUDIO          |

| SDIO_CARD             | I/O | SDIO_D2        | P41 | S42 | I2S0_CK                   | I/O | AUDIO          |

| SDIO_CARD             | I/O | SDIO_D3        | P42 | S43 | ESPI_ALERTO#              | 1   | ESPI INTERFACE |

| SPI 0 INTERFACE       | 0   | SPI0_CS0#      | P43 | S44 | ESPI_ALERT1#              | I   | ESPI INTERFACE |

| SPI 0 INTERFACE       | 0   | SPIO_CK        | P44 | S45 | MDIO_CLK/JTAG_TDI         | 0   | SERDES         |

| SPI 0 INTERFACE       | I   | SPIO_DIN       | P45 | S46 | MDIO_DAT/JTAG_TDO         | I/O | SERDES         |

|                       |     |                |     |     |                           |     |                |

| SPI 0 INTERFACE         | 0   | SPI0_DO               | P46 | S47 | GND                  |     |                |

|-------------------------|-----|-----------------------|-----|-----|----------------------|-----|----------------|

|                         |     | GND                   | P47 | S48 | I2C_GP_CK            | I/O | I2C            |

| SATA                    | 0   | SATA_TX+              | P48 | S49 | I2C_GP_DAT           | I/O | I2C            |

| SATA                    | 0   | SATA_TX-              | P49 | S50 | I2S2_LRCK / HDA_SYNC | I/O | I2S / HD AUDIO |

|                         |     | GND                   | P50 | S51 | I2S2_SDOUT / HDA_SDO | 0   | I2S / HD AUDIO |

| SATA                    | 1   | SATA_RX+              | P51 | S52 | I2S2_SDIN / HDA_SDI  | I   | I2S / HD AUDIO |

| SATA                    | I   | SATA_RX-              | P52 | S53 | I2S2_CK / HDA_CK     | 0   | I2S / HD AUDIO |

|                         |     | GND                   | P53 | S54 | SATA_ACT#            | 0   | SATA           |

| SPI 1 / eSPI INTERFACE  | 0   | SPI1_CS0#/ESPI_CS0#   | P54 | S55 | USB5_EN_OC#          | I/O | USB            |

| SPI 1 / eSPI INTERFACE  |     | SPI1_CS1#/ESPI_CS1#   | P55 | S56 | ESPI_IO_2            | I/O | eSPI INTERFACE |

| SPI 1 / eSPI INTERFACE  | 0   | SPI1_CK / ESPI_CK     | P56 | S57 | ESPI_IO_3            | I/O | eSPI INTERFACE |

| SPI 1 / eSPI INTERFACE  | I/O | SPI1_DIN / ESPI_IO_1  | P57 | S58 | ESPI_RESET#          | 0   | eSPI INTERFACE |

| SPI 1 / eSPI INTERFACE  | I/O | SPI1_DO / ESPI_IO_0   | P58 | S59 | USB5+                | I/O | USB            |

|                         |     | GND                   | P59 | S60 | USB5-                | I/O | USB            |

| USB                     | I/O | USB0+                 | P60 | S61 | GND                  |     |                |

| USB                     | I/O | USB0-                 | P61 | S62 | USB3_SSTX+           | 0   | USB            |

| USB                     | I/O | USB0_EN_OC#           | P62 | S63 | USB3_SSTX-           | 0   | USB            |

| USB                     |     | USB0_VBUS_DET         | P63 | S64 | GND                  |     |                |

| USB                     |     | USB0_OTG_ID           | P64 | S65 | USB3_SSRX+           | I   | USB            |

| USB                     | I/O | USB1+                 | P65 | S66 | USB3_SSRX-           |     | USB            |

| USB                     | I/O | USB1-                 | P66 | S67 | GND                  |     |                |

| USB                     | I/O | USB1_EN_OC#           | P67 | S68 | USB3+                | I/O | USB            |

|                         |     | GND                   | P68 | S69 | USB3-                | I/O | USB            |

| USB                     | I/O | USB2+                 | P69 | S70 | GND                  |     |                |

| USB                     | I/O | USB2-                 | P70 | S71 | USB2_SSTX+           | 0   | USB            |

| USB                     | I/O | USB2_EN_OC#           | P71 | S72 | USB2_SSTX-           | 0   | USB            |

| Reserved Purpose Signal | I/O | RSVD#P72 (JTAG_RST#)  | P72 | S73 | GND                  |     |                |

| Reserved Purpose Signal | I/O | RSVD#P73 (JTAG_TRST#) | P73 | S74 | USB2_SSRX+           | I   | USB            |

| USB                     | I/O | USB3_EN_OC#           | P74 | S75 | USB2_SSRX-           | I   | USB            |

| PCI_e                   | 0   | PCIE_A_RST#           | P75 | S76 | PCIE_B_RST#          | 0   | PCI-e          |

|                         |     |                       |     |     |                      |     |                |

| USB                    | I/O | USB4_EN_OC#               | P76  | S77  | PCIE_C_RST#                 | 0   | PCI-e             |

|------------------------|-----|---------------------------|------|------|-----------------------------|-----|-------------------|

| PCI-e                  | Ι   | PCIE_B_CLKREQ# (JTAG_TMS) | P77  | S78  | SERDES_1_RX+ / PCIE_C_RX+   | I   | SERDES / PCI-e    |

| PCI-e                  | I   | PCIE_A_CLKREQ# (JTAG_TCK) | P78  | S79  | SERDES_1_RX- / PCIE_C_RX- I |     | SERDES / PCI-e    |

|                        |     | GND                       | P79  | S80  | GND                         |     | PCI-e             |

| PCI-e                  | 0   | PCIE_C_REFCK+             | P80  | S81  | SERDES_1_TX+ / PCIE_C_TX+   | 0   | SERDES / PCI-e    |

| PCI-e                  | 0   | PCIE_C_REFCK-             | P81  | S82  | SERDES_1_TX- / PCIE_C_TX-   | 0   | SERDES / PCI-e    |

|                        |     | GND                       | P82  | S83  | GND                         |     |                   |

| PCI-e                  | 0   | PCIE_A_REFCK+             | P83  | S84  | PCIE_B_REFCK+               | 0   | PCI-e             |

| PCI-e                  | 0   | PCIE_A_REFCK-             | P84  | S85  | PCIE_B_REFCK-               | 0   | PCI-e             |

|                        |     | GND                       | P85  | S86  | GND                         |     |                   |

| PCI-e                  | I   | PCIE_A_RX+                | P86  | S87  | PCIE_B_RX+                  | 1   | PCI-e             |

| PCI-e                  | I   | PCIE_A_RX-                | P87  | S88  | PCIE_B_RX-                  | I   | PCI-e             |

|                        |     | GND                       | P88  | S89  | GND                         |     |                   |

| PCI-e                  | 0   | PCIE_A_TX+                | P89  | S90  | PCIE_B_TX+                  | 0   | PCI-e             |

| PCI-e                  | 0   | PCIE_A_TX-                | P90  | S91  | PCIE_B_TX-                  | 0   | PCI-e             |

|                        |     | GND                       | P91  | S92  | GND                         |     |                   |

| HDMI/DP++ INTERFACE #1 | 0   | HDMI_D2+ / DP1_LANE0+     | P92  | S93  | DP0_LANE0+                  | 0   | DP++ INTERFACE #0 |

| HDMI/DP++ INTERFACE #1 | 0   | HDMI_D2- / DP1_LANE0-     | P93  | S94  | DP0_LANE0-                  | 0   | DP++ INTERFACE #0 |

|                        |     | GND                       | P94  | S95  | DP0_AUX_SEL                 | I   | DP++ INTERFACE #0 |

| HDMI/DP++ INTERFACE #1 | 0   | HDMI_D1+ / DP1_LANE1+     | P95  | S96  | DP0_LANE1+                  | 0   | DP++ INTERFACE #0 |

| HDMI/DP++ INTERFACE #1 | 0   | HDMI_D1- / DP1_LANE1-     | P96  | S97  | DP0_LANE1-                  | 0   | DP++ INTERFACE #0 |

|                        |     | GND                       | P97  | S98  | DP0_HPD                     | I   | DP++ INTERFACE #0 |

| HDMI/DP++ INTERFACE #1 | 0   | HDMI_D0+ / DP1_LANE2+     | P98  | S99  | DP0_LANE2+                  | 0   | DP++ INTERFACE #0 |

| HDMI/DP++ INTERFACE #1 | 0   | HDMI_D0- / DP1_LANE2-     | P99  | S100 | DP0_LANE2-                  | 0   | DP++ INTERFACE #0 |

|                        |     | GND                       | P100 | S101 | GND                         |     |                   |

| HDMI/DP++ INTERFACE #1 | 0   | HDMI_CK+/ DP1_LANE3+      | P101 | S102 | DP0_LANE3+                  | 0   | DP++ INTERFACE #0 |

| HDMI/DP++ INTERFACE #1 | 0   | HDMI_CK- / DP1_LANE3-     | P102 | S103 | DP0_LANE3-                  | 0   | DP++ INTERFACE #0 |

|                        |     | GND                       | P103 | S104 | USB3_OTG_ID                 | I   | USB               |

| HDMI/DP++ INTERFACE #1 | I   | HDMI_HPD / DP1_HPD        | P104 | S105 | DP0_AUX+                    | I/O | DP++ INTERFACE #0 |

| HDMI/DP++ INTERFACE #1 | I/O | HDMI_CTRL_CK/DP1_AUX+     | P105 | S106 | DP0_AUX-                    | I/O | DP++ INTERFACE #0 |

|                        |     |                           |      |      |                             |     |                   |

| HDMI/DP++ INTERFACE #1 | I/O | HDMI_CTRL_DAT/DP1_AUX- | P106 | S107 | LCD1_BKLT_EN                       | 0   | LCD_SUPPORT     |

|------------------------|-----|------------------------|------|------|------------------------------------|-----|-----------------|

| HDMI/DP++ INTERFACE #1 | I   | DP1_AUX_SEL            | P107 | S108 | LVDS1_CK+ / eDP1_AUX+<br>DSI1_CLK+ | / 0 | PRIMARY_DISPLAY |

| GPIO / CSI 0 CAMERA    | I/O | GPIO0 / CAM0_PWR#      | P108 | S109 | LVDS1_CK- / eDP1_AUX-<br>DSI1_CLK- | / 0 | PRIMARY_DISPLAY |

| GPIO / CSI 1 CAMERA    | I/O | GPIO1 / CAM1_PWR#      | P109 | S110 | GND                                |     |                 |

| GPIO / CSI 0 CAMERA    | I/O | GPIO2 / CAMO_RST#      | P110 | S111 | LVDS1_0+ / eDP1_TX0+<br>DSI1_D0+   | / 0 | PRIMARY_DISPLAY |

| GPIO / CSI 1 CAMERA    | I/O | GPIO3 / CAM1_RST#      | P111 | S112 | LVDS1_0- / eDP1_TX0-<br>DSI1_D0-   | / 0 | PRIMARY_DISPLAY |

| GPIO / HDA AUDIO       | I/O | GPIO4 / HDA_RST#       | P112 | S113 | eDP0_HPD                           | I   | PRIMARY_DISPLAY |

| GPIO                   | I/O | GPIO5 / PWM_OUT        | P113 | S114 | LVDS1_1+ / eDP1_TX1+<br>DSI1_D1+   | / 0 | PRIMARY_DISPLAY |

| GPIO                   | I/O | GPIO6 / TACHIN         | P114 | S115 | LVDS1_1- / eDP1_TX1-<br>DSI1_D1-   | / 0 | PRIMARY_DISPLAY |

| GPIO                   | I/O | GPIO7                  | P115 | S116 | LCD1_VDD_EN                        | 0   | LCD_SUPPORT     |

| GPIO                   | I/O | GPIO8                  | P116 | S117 | LVDS1_2+ / eDP1_TX2+<br>DSI1_D2+   | / 0 | PRIMARY_DISPLAY |

| GPIO                   | I/O | GPIO9                  | P117 | S118 | LVDS1_2- / eDP1_TX2-<br>DSI1_D2-   | / 0 | PRIMARY_DISPLAY |

| GPIO                   | I/O | GPIO10                 | P118 | S119 | GND                                |     |                 |

| GPIO                   | I/O | GPIO11                 | P119 | S120 | LVDS1_3+ / eDP1_TX3+<br>DSI1_D3+   | / 0 | PRIMARY_DISPLAY |

|                        |     | GND                    | P120 | S121 | LVDS1_3- / eDP1_TX3-<br>DSI1_D3-   | / 0 | PRIMARY_DISPLAY |

| MANAGEMENT             | I/O | I2C_PM_CK              | P121 | S122 | LCD1_BKLT_PWM                      | 0   | LCD_SUPPORT     |

| MANAGEMENT             | I/O | I2C_PM_DAT             | P122 | S123 | GPIO13                             | I/O | GPIO            |

| BOOT_SEL               | I   | BOOT_SELO#             | P123 | S124 | GND                                |     |                 |

| BOOT_SEL               | I   | BOOT_SEL1#             | P124 | S125 | LVDS0_0+ / eDP0_TX0+<br>DSI0_D0+   | / 0 | PRIMARY_DISPLAY |

| BOOT_SEL               | I   | BOOT_SEL2#             | P125 | S126 | LVDS0_0- / eDP0_TX0-<br>DSI0_D0-   | / 0 | PRIMARY_DISPLAY |

| MANAGEMENT             | 0   | RESET_OUT#             | P126 | S127 | LCD0_BKLT_EN                       | 0   | LCD_SUPPORT     |

| MANAGEMENTIRESET_IN#P127S128LVDSO_1+ / eDPO_TX1+ / OPRIMARY_DISPLAYMANAGEMENTIPOWER_BTN#P128S129LVDSO_1+ / eDPO_TX1+ / OPRIMARY_DISPLAYASYNC_SERIALOSER0_TXP129S130GNDASYNC_SERIALISER0_RXP130S131LVDSO_2+ / eDPO_TX2+ / OPRIMARY_DISPLAYASYNC_SERIALOSER0_RTS#P130S132LVDSO_2+ / eDPO_TX2+ / OPRIMARY_DISPLAYASYNC_SERIALOSER0_RTS#P131S132LVDSO_2+ / eDPO_TX2+ / OPRIMARY_DISPLAYASYNC_SERIALISER0_CTS#P132S133LCD0_VDD_ENOLCD_SUPPORTASYNC_SERIALISER1_TXP134S135LVDSO_CK+ / eDPO_AUX+ / OPRIMARY_DISPLAYASYNC_SERIALOSER1_TXP136S137LVDSO_3+ / eDPO_TX3+ / OPRIMARY_DISPLAYASYNC_SERIALISER2_TXP136S137LVDSO_3+ / eDPO_TX3+ / OPRIMARY_DISPLAYASYNC_SERIALISER2_RXP136S137LVDSO_3+ / eDPO_TX3+ / OPRIMARY_DISPLAYASYNC_SERIALOSER2_RTS#P138S139I2C_LCD_CKOLCD_SUPPORTASYNC_SERIALISER2_RTS#P138S139I2C_LCD_DATI/OLCD_SUPPORTASYNC_SERIALOSER3_TXP140S141LCD0_URLT_PWMOLCD_SUPPORTASYNC_SERIALISER3_RXP140S141LCD0_LBKLT_PWMOLCD_SUPPORTASYNC_S    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASYNC_SERIALOSERO_TXP129S130GNDASYNC_SERIALISERO_RXP130S131LVDSO_2+ / eDPO_TX2+ / 0PRIMARY_DISPLAYASYNC_SERIALOSERO_RTS#P131S132LVDSO_2- / eDPO_TX2- / 0PRIMARY_DISPLAYASYNC_SERIALISERO_CTS#P132S133LCDO_VDD_ENOLCD_SUPPORTASYNC_SERIALISERO_CTS#P132S134LVDSO_CK+ / eDPO_AUX+ / 0PRIMARY_DISPLAYASYNC_SERIALISER1_TXP134S135LVDSO_CK+ / eDPO_AUX+ / 0PRIMARY_DISPLAYASYNC_SERIALISER1_RXP135S136GNDS137LVDSO_SA+ / eDPO_TX3+ / 0PRIMARY_DISPLAYASYNC_SERIALISER2_TXP136S137LVDSO_3+ / eDPO_TX3+ / 0PRIMARY_DISPLAYASYNC_SERIALISER2_RXP136S137LVDSO_3+ / eDPO_TX3+ / 0PRIMARY_DISPLAYASYNC_SERIALISER2_RXP138S139LVDSO_3+ / eDPO_TX3+ / 0PRIMARY_DISPLAYASYNC_SERIALISER2_RTS#P138S139LVDSO_3+ / eDPO_TX3+ / 0PRIMARY_DISPLAYASYNC_SERIALISER2_RTS#P138S139I2C_LCD_CK0LCD_SUPPORTASYNC_SERIALISER3_TXP140S141LCD0_BKI_PWM0LCD_SUPPORTASYNC_SERIALISER3_RXP140S143GNDLCD_SUPPORTICD_SUPPORTASYNC_SERIALISER3_RXP140S141LCD0_BKI_PWM0LCD_SUPPORT </td |

| ASYNC_SERIALISER0_RXP130S131LVDS0_2+/eDP0_TX2+/OPRIMARY_DISPLAYASYNC_SERIAL0SER0_RTS#P131S132LVDS0_2-/eDP0_TX2-/OPRIMARY_DISPLAYASYNC_SERIALISER0_CTS#P132S133LCD0_VDD_ENOLCD_SUPPORTGNDP133S134LVDS0_CK+/eDP0_AUX+/OPRIMARY_DISPLAYASYNC_SERIAL0SER1_TXP133S134LVDS0_CK+/eDP0_AUX+/OPRIMARY_DISPLAYASYNC_SERIAL1SER1_RXP135S136GNDASYNC_SERIALOPRIMARY_DISPLAYDSI0_CLK+ASYNC_SERIAL0SER2_TXP136S137LVDS0_S+/eDP0_TX3+/OPRIMARY_DISPLAYASYNC_SERIAL1SER2_RXP136S137LVDS0_3+/eDP0_TX3+/OPRIMARY_DISPLAYASYNC_SERIAL0SER2_RXP136S137LVDS0_3+/eDP0_TX3+/OPRIMARY_DISPLAYASYNC_SERIAL1SER2_RXP136S139I2C_LCD_CKOLCD_SUPPORTASYNC_SERIAL0SER3_TXP140S141LCD0_BKLT_PWMOLCD_SUPPORTASYNC_SERIAL1SER3_RXP140S141LCD0_BKLT_PWMOLCD_SUPPORTASYNC_SERIAL1SER3_RXP140S141LCD0_BKLT_PWMOLCD_SUPPORTASYNC_SERIAL1 <td< td=""></td<>                                                                                                                                 |

| DSI0_D2+ASYNC_SERIALOSER0_RTS#P131S132LVDS0_2- / eDP0_TX2- / OPRIMARY_DISPLAYASYNC_SERIALISER0_CTS#P132S133LCD0_VDD_ENOLCD_SUPPORTASYNC_SERIALISER1_TXP133S134LVDS0_CK+ / eDP0_AUX+ / OPRIMARY_DISPLAYASYNC_SERIALOSER1_TXP134S135LVDS0_CK- / eDP0_AUX- / OPRIMARY_DISPLAYASYNC_SERIALISER1_RXP135S136GNDASYNC_SERIALISER2_TXP136S137LVDS0_3+ / eDP0_TX3+ / OPRIMARY_DISPLAYASYNC_SERIALOSER2_RXP136S137LVDS0_3+ / eDP0_TX3+ / OPRIMARY_DISPLAYASYNC_SERIALISER2_RXP136S139LVDS0_3+ / eDP0_TX3+ / OPRIMARY_DISPLAYASYNC_SERIALOSER2_RXP138S139I2C_LCD_CKOLCD_SUPPORTASYNC_SERIALISER2_CTS#P139S140I2C_LCD_DATI/OLCD_SUPPORTASYNC_SERIALISER3_TXP140S141LCD0_BKLT_PWMOLCD_SUPPORTASYNC_SERIALISER3_RXP141S142GPI012I/OGPI0                                                                                                                                                                                                                             |

| ASYNC_SERIALISER0_CTS#P132S133LCD0_VDD_ENOLCD_SUPPORTGNDP133S134LVDS0_CK+ / eDP0_AUX+ / 0PRIMARY_DISPLAYASYNC_SERIALOSER1_TXP134S135LVDS0_CK- / eDP0_AUX- / 0PRIMARY_DISPLAYASYNC_SERIALISER1_RXP135S136GNDASYNC_SERIALISER2_TXP136S137LVDS0_3+ / eDP0_TX3+ / 0PRIMARY_DISPLAYASYNC_SERIALISER2_RXP137S138LVDS0_3+ / eDP0_TX3+ / 0PRIMARY_DISPLAYASYNC_SERIALOSER2_RXP137S138LVDS0_3- / eDP0_TX3- / 0PRIMARY_DISPLAYASYNC_SERIALOSER2_RXP138S139I2C_LCD_CKOLCD_SUPPORTASYNC_SERIALISER2_CTS#P139S140I2C_LCD_DATI/OLCD_SUPPORTASYNC_SERIALISER3_TXP140S141LCD0_BKLT_PWMOLCD_SUPPORTASYNC_SERIALISER3_RXP141S142GPI012I/OGPI0                                                                                                                                                                                                                                                                                                                           |