# **Com express**

## User Manual

## CCOMe-C96

Carrier Board for COM-Express<sup>™</sup> Type 6 Module on ATX form factor

www.seco.com

## **REVISION HISTORY**

| Revision | Date                        | Note          | Rif |

|----------|-----------------------------|---------------|-----|

| 1.0      | 2 <sup>nd</sup> August 2021 | First release | AR  |

|          |                             |               |     |

|          |                             |               |     |

#### All rights reserved. All information contained in this manual is proprietary and confidential material of SECO S.p.A.

Unauthorised use, duplication, modification or disclosure of the information to a third-party by any means without prior consent of SECO S.p.A. is prohibited.

Every effort has been made to ensure the accuracy of this manual. However, SECO S.p.A. accepts no responsibility for any inaccuracies, errors or omissions herein. SECO S.p.A. reserves the right to change precise specifications without prior notice to supply the best product possible.

For further information on this module or other SECO products, but also to get the required assistance for any and possible issues, please contact us using the dedicated web form available at <a href="https://www.seco.com/">https://www.seco.com/</a> (registration required).

Our team is ready to assist you.

## INDEX

| Chapter 1.     | INTRODUCTION                                        | 5 |

|----------------|-----------------------------------------------------|---|

| 1.1 Wa         | /arranty                                            | 6 |

| 1.2 Inf        | formation and assistance                            | 7 |

| 1.3 RN         | MA number request                                   | 7 |

| 1.4 Sa         | afety                                               | 8 |

| 1.5 El€        | ectrostatic Discharges                              | 8 |

| 1.6 Rc         | oHS compliance                                      | 8 |

| 1.7 Sa         | afety Policy                                        | 9 |

| 1.8 Te         | erminology and definitions1                         | 0 |

| 1.9 Re         | eference specifications                             | 2 |

| Chapter 2.     | OVERVIEW                                            | 3 |

| 2.1 Int        | troduction1                                         | 4 |

| 2.2 Te         | echnical Specifications1                            | 5 |

| 2.3 Ele        | ectrical Specifications1                            | 6 |

| 2.3.1          | Smart Battery SM Bus Connector1                     | 8 |

| 2.3.2          | RTC Battery1                                        |   |

| 2.3.3          | Power Rails meanings                                |   |

|                | echanical Specifications                            |   |

|                | ock Diagram2                                        |   |

| Chapter 3.     | CONNECTORS                                          | 2 |

| 3.1 Co         | onnectors placement2                                | 3 |

| 3.2 Co         | onnectors overview                                  |   |

| 3.2.1          | Connectors list2                                    |   |

| 3.2.2          | Jumpers and switch list                             |   |

|                | onnectors description                               |   |

| 3.3.1          | COM Express <sup>™</sup> module connectors          |   |

| 3.3.2          | PCI-e x4 Slots                                      |   |

| 3.3.3          | PEG (PCI Express Graphics x16) Connector            |   |

| 3.3.4<br>3.3.5 | eSPI/LPC Debug Connector                            |   |

| 0.0.0          | Control poits and R3232 poits internal pill readers | 4 |

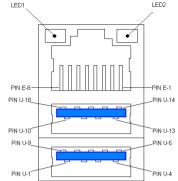

| 3.3.6     | USB and Gigabit Ethernet ports          | Ś |

|-----------|-----------------------------------------|---|

| 3.3.7     | S-ATA Connectors                        | ) |

| 3.3.8     |                                         |   |

| 3.3.9     | External BIOS SPI Flash header          | 2 |

| 3.3.10    | 0 BIOS disable signals                  | 3 |

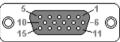

| 3.3.11    | 1 VGA Connector                         | 3 |

| 3.3.12    | 2 FuSa Header                           | 1 |

| 3.3.13    | 3 GPIO pin header / microSD Card Slot   | Ś |

| 3.3.14    |                                         |   |

| 3.3.15    | 5 External EEPROM I2C Flash socket      | 3 |

| 3.3.16    | • • • • • • • • • • • • • • • • • • • • |   |

| 3.3.17    | 7 eDP Connector                         | ) |

| 3.3.18    | 6 LVDS Connector                        | I |

| 3.3.19    |                                         |   |

| 3.3.20    |                                         | 1 |

| 3.3.21    | 1 JTAG Connector                        | 1 |

| 3.3.22    | 2 FAN Connector                         | 1 |

| 3.3.23    |                                         | 5 |

| Chapter 4 | Appendices                              | ) |

| 4.1 TI    | Fhermal Design                          | 1 |

| 4.2 A     | Accessories                             | 3 |

## Chapter 1. INTRODUCTION

- Warranty

- Information and assistance

- RMA number request

- Safety

- Electrostatic Discharges

- RoHS compliance

- Safety Policy

- Terminology and definitions

- Reference specifications

## 1.1 Warranty

This product is subject to the Italian Law Decree 24/2002, acting European Directive 1999/44/CE on matters of sale and warranties to consumers. The warranty on this product lasts 1 year.

Under the warranty period, the Supplier guarantees the buyer assistance and service for repairing, replacing or credit of the item, at the Supplier's own discretion.

Shipping costs that apply to non-conforming items or items that need replacement are to be paid by the customer.

Items cannot be returned unless previously authorised by the supplier.

The authorisation is released after completing the specific form available on the web-site <u>https://www.seco.com/eu/support/online-rma.html</u> (Online RMA). The RMA Authorisation number must be put both on the packaging and on the documents shipped with the items, which must include all the accessories in their original packaging, with no signs of damage to, or tampering with, any returned item.

The error analysis form identifying the fault type must be completed by the customer and must accompany the returned item.

If any of the above mentioned requirements for RMA is not satisfied, the item will be shipped back and the customer will have to pay any and all shipping costs.

Following after a technical analysis, the supplier will verify if all the requirements for which a warranty service applies are met. If the warranty cannot be applied, the Supplier will calculate the minimum cost of this initial analysis on the item and the repair costs. Costs for replaced components will be calculated separately.

Warning! All changes or modifications to the equipment not explicitly approved by SECO S.p.A. could impair the equipment's functionality and could void the warranty.

## 1.2 Information and assistance

What do I have to do if the product is faulty?

SECO S.p.A. offers the following services:

- SECO website: visit <u>https://www.seco.com</u> to receive the latest information on the product. In most cases it is possible to find useful information to solve the problem.

- SECO Sales Representative: the Sales Rep can help to determine the exact cause of the problem and search for the best solution.

- SECO Help-Desk: contact SECO Technical Assistance. A technician is at disposal to understand the exact origin of the problem and suggest the correct solution.

E-mail: technical.service@seco.com

Fax (+39) 0575 340434

- Repair centre: it is possible to send the faulty product to the SECO Repair Centre. In this case, follow this procedure:

- o Returned items must be accompanied by a RMA Number. Items sent without the RMA number will be not accepted.

- Returned items must be shipped in an appropriate package. SECO is not responsible for damages caused by accidental drop, improper usage, or customer neglect.

Note: Please have the following information before asking for technical assistance:

- Name and serial number of the product;

- Description of Customer's peripheral connections;

- Description of Customer's software (operating system, version, application software, etc.);

- A complete description of the problem;

- The exact words of every kind of error message encountered.

## 1.3 RMA number request

To request a RMA number, please visit SECO's web-site. On the home page, please select "RMA Online" and follow the procedure described.

A RMA Number will be released within 1 working day (only for on-line RMA requests).

## 1.4 Safety

The CCOMe-C96 board uses only extremely-low voltages.

While handling the board, please use extreme caution to avoid any kind of risk or damages to electronic components.

Always switch the power off, and unplug the power supply unit, before handling the board and/or connecting cables or other boards.

Avoid using metallic components - like paper clips, screws and similar - near the board when connected to a power supply, to avoid short circuits due to unwanted contacts with other board components.

If the board has become wet, never connect it to any external power supply unit or battery.

Check carefully that all cables are correctly connected and that they are not damaged.

### 1.5 Electrostatic Discharges

The CCOMe-C96 board, like any other electronic product, is an electrostatic sensitive device: high voltages caused by static electricity could damage some or all the devices and/or components on-board.

Whenever handling a CCOMe-C96 board, ground yourself through an anti-static wrist strap. Placement of the board on an anti-static surface is also highly recommended.

### 1.6 RoHS compliance

The CCOMe-C96 board is designed using RoHS compliant components and is manufactured on a lead-free production line. It is therefore fully RoHS compliant.

## 1.7 Safety Policy

In order to meet the safety requirements of EN62368-1:2014 standard for Audio/Video, information and communication technology equipment, the CCOMe-C96 Carrier Board shall be:

- used inside a fire enclosure made of non-combustible material or V-1 material (the fire enclosure is not necessary if the maximum power supplied to the board never exceeds 100 W, even in worst-case fault);

- used inside an enclosure provided with the symbol IEC 60417-5041 (element 1a according to clause 9.5.2 of the IEC 62368-1) on the external part;

- installed inside an enclosure compliant with all applicable IEC 62368-1 requirements;

The manufacturer which includes a CCOMe-C96 Carrier Board in his end-user product shall:

- verify the compliance with B.2 and B.3 clauses of the EN62368-1 standard when the module works in its own final operating condition

- prescribe temperature and humidity range for operating, transport and storage conditions;

- prescribe to perform maintenance on the board only when it is off and has already cooled down;

- prescribe that the connections from or to the board have to be compliant to ES1 requirements;

- the board in its enclosure must be evaluated for temperature and airflow considerations.

## 1.8 Terminology and definitions

| ACPI     | Advanced Configuration and Power Interface, an open industrial standard for the board's devices configuration and power management                                         |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIOS     | Basic Input / Output System, the Firmware Interface that initializes the board before the OS starts loading                                                                |

| CEC      | Consumer Electronics Control, an HDMI feature which allows controlling more devices connected together by using only one remote control                                    |

| DDC      | Display Data Channel, a kind of I2C interface for digital communication between displays and graphics processing units (GPU)                                               |

| DP       | Display Port, a type of digital video display interface                                                                                                                    |

| DVI      | Digital Visual interface, a type of digital video display interface                                                                                                        |

| eDP      | embedded Display Port, a type of digital video display interface developed especially for internal connections between boards and digital displays                         |

| GbE      | Gigabit Ethernet                                                                                                                                                           |

| Gbps     | Gigabits per second                                                                                                                                                        |

| GND      | Ground                                                                                                                                                                     |

| GPI/O    | General purpose Input/Output                                                                                                                                               |

| HD Audio | High Definition Audio, most recent standard for hardware codecs developed by Intel® in 2004 for higher audio quality                                                       |

| HDMI     | High Definition Multimedia Interface, a digital audio and video interface                                                                                                  |

| I2C Bus  | Inter-Integrated Circuit Bus, a simple serial bus consisting only of data and clock line, with multi-master capability                                                     |

| JTAG     | Joint Test Action Group, common name of IEEE1149.1 standard for testing printed circuit boards and integrated circuits through the Debug port                              |

| LPC Bus  | Low Pin Count Bus, a low speed interface based on a very restricted number of signals, deemed to management of legacy peripherals                                          |

| LVDS     | Low Voltage Differential Signalling, a standard for transferring data at very high speed using inexpensive twisted pair copper cables, usually used for video applications |

| Mbps     | Megabits per second                                                                                                                                                        |

| N.A.     | Not Applicable                                                                                                                                                             |

| N.C.     | Not Connected                                                                                                                                                              |

| OS       | Operating System                                                                                                                                                           |

| PCI-e    | Peripheral Component Interface Express                                                                                                                                     |

| PWM      | Pulse Width Modulation                                                                                                                                                     |

| PWR      | Power                                                                                                                                                                      |

| SATA     | Serial Advance Technology Attachment, a differential half duplex serial interface for Hard Disks                                                                           |

| SD       | Secure Digital, a memory card type                                                                                                                                         |

| SDIO     | Secure Digital Input/Output, an evolution of the SD standard that allows use the use of the same SD interface to drive different Input/Output                              |

devices, like cameras, GPS, Tuners and so on

- SIM Subscriber Identity Module, a card which stores all data of the owner necessary to allow him accessing to mobile communication networks

- SM Bus System Management Bus, a subset of the I2C bus protocol dedicated to communication with devices for system management, like a smart battery and other power supply-related devices

- SPI Serial Peripheral Interface, a 4-Wire synchronous full-duplex serial interface which is composed of a master and one or more slaves, individually enabled through a Chip Select line

- TBM To be measured

- TMDS Transition-Minimized Differential Signalling, a method for transmitting high speed serial data, normally used on DVI and HDMI interfaces

- TTL Transistor-transistor Logic

- UIM User Identity Module, an extension of SIM modules.

- USB Universal Serial Bus

- V\_REF Voltage reference Pin

## 1.9 Reference specifications

Here below it is a list of applicable industry specifications and reference documents.

| Reference                                          | Link                                                                                                                       |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| ACPI                                               | http://www.acpi.info                                                                                                       |

| Com Express <sup>™</sup>                           | https://www.picmg.org/openstandards/com-express/                                                                           |

| Com Express <sup>™</sup> Carrier Design Guide      | https://www.picmg.org/wp-content/uploads/PICMG_COMDG_2.0-RELEASED-2013-12-061.pdf                                          |

| DDC                                                | https://www.vesa.org/                                                                                                      |

| DP, eDP                                            | https://www.vesa.org/                                                                                                      |

| Ethernet                                           | http://standards.ieee.org/about/get/802/802.3.html                                                                         |

| HD Audio                                           | http://www.intel.com/content/dam/www/public/us/en/documents/product-specifications/high-definition-audio-specification.pdf |

| HDMI                                               | http://www.hdmi.org/index.aspx                                                                                             |

| 12C                                                | http://www.nxp.com/docs/en/user-guide/UM10204.pdf                                                                          |

| Intel <sup>®</sup> Front Panel I/O connectivity DG | http://www.formfactors.org/developer/specs/A2928604-005.pdf                                                                |

| LPC Bus                                            | http://www.intel.com/design/chipsets/industry/lpc.htm                                                                      |

| LVDS                                               | http://www.ti.com/lit/ug/snla187/snla187.pdf                                                                               |

| PCI Express                                        | http://www.pcisig.com/specifications/pciexpress                                                                            |

| SATA                                               | https://www.sata-io.org                                                                                                    |

| SD Card Association                                | https://www.sdcard.org                                                                                                     |

| SM Bus                                             | http://www.smbus.org/specs                                                                                                 |

| TMDS                                               | http://www.latticesemi.com/view_document?document_id=38351                                                                 |

| USB 2.0 and USB OTG                                | http://www.usb.org/developers/docs/usb20_docs/usb_20_080117.zip                                                            |

| USB 3.0                                            | http://www.usb.org/developers/docs/usb_31_080117.zip                                                                       |

## Chapter 2. OVERVIEW

- Introduction

- Technical Specifications

- Electrical Specifications

- Mechanical Specifications

- Block Diagram

## 2.1 Introduction

CCOMe-C96 is a carrier board, designed in ATX form factor, intended for the use with COM-Express<sup>™</sup> Type 6 CPU modules.

COM-Express<sup>™</sup> is an open industry standard defined specifically for COMs (computer on modules). Its definition provides the ability to make a smooth transition from legacy parallel interfaces to the newest technologies based on serial buses available today.

COM Express<sup>M</sup> CPU modules integrate all the core components of a typical PC-like architecture, and make all interface available through two standardized connectors, so that COM Express<sup>M</sup> modules become scalable. This means that once an application has been created, there is the ability to diversify the product range through the use of different performance class or form factor size modules.

Baseboard designers can use just the I/O interfaces that really need, providing, on the carrier board, the routing to the adequate interface connectors.

This versatility allows the designer to create a dense and optimised package, which results in a more reliable product while simplifying system integration.

CCOMe-C96 board can be used both as an evaluation module, to test the functionality of your COM-Express<sup>™</sup> module and design an application specific carrier board for it, or as a complete carrier board, already suited for standard purposes, with a small space consumption.

In any case, the solutions so realised is fully scalable, and allows to the user to keep his own-designed system continuously up-to-date, since the system can be updated simply replacing the COM-Express<sup>™</sup> module with a newer one, just unplugging the module and replacing it, without the need of redesigning it.

The robust thermal and mechanical concept, combined with extended power-management capabilities, is perfectly suited for all applications.

### 2.2 Technical Specifications

Supported Modules COM Express<sup>™</sup> Type 6 compliant modules Mass Storage interfaces 4x SATA 7p M connectors µSD Card slot (interface multiplexed with GPIO header) Video Interfaces  $3 \times DP++$  connectors VGA connector LVDS 24-bit Single/Dual Channel Connector LVDS External EDID flash socket eDP 4-lanes 40 poles VESA connector Audio On-board HD Audio Codec (Cirrus Logic CS4207) Mic In + Line Out internal pin header HD Audio Jacks S/PDIF Out Optical connector

#### USB

4 x USB 3.1 Host ports on Type-A sockets 4 x USB 2.0 Host ports on Quad Type-A sockets

#### Networking

1x RJ-45 connector

#### PCI-e

2x PCI-e x4 Slots

1x PCI-e x16 Slot

#### Serial Ports

2 x RS-232 / RS-422 / RS-485 ports on internal pin header (from carrier board's LPC Dual UART controller)

2 x RS-232 ports on dedicated pin header (from module)

#### Other Interfaces

4 x GPI + 4 x GPO pin header (interface multiplexed with µSD slot) SPI Flash header Button / LEDs front panel header 4-pin tachometric FAN connector I2C + SM Bus on feature Pin header FuSa Header I2C Flash Socket JTAG connector LPC internal header USB overcurrent header SM Bus Smart Battery Connector 4 x 7-segment LCD displays for POST codes LPC/eSPI internal header Power supply: ATX 24 poles connector for carrier board working only Auxiliary 12V connector for carrier board working only 12 V<sub>DC</sub> power in connector for COM Express<sup>™</sup> module's working Coin-cell holder for RTC Operating temperature:  $0^{\circ}C \div +60^{\circ}C^{*}$  (Commercial version) Dimensions: 305x244mm (ATXform factor, 12" x 9.6")

\* Temperature ranges indicated mean that all components available onboard are certified for working with a Tcase included in these temperature ranges. This means that it is customer's responsibility to ensure that all components' Tcases remain in the range above indicated. Please also check paragraph 4.1.

## 2.3 Electrical Specifications

CCOMe-C96 board needs to be supplied using a standard ATX Power Supply, which can, however, also be configured to work in AT mode.

| ATX/ AT Power Connector – CN10 |            |     |           |

|--------------------------------|------------|-----|-----------|

| Pin                            | Signal     | Pin | Signal    |

| 1                              | +3.3V_RUN  | 13  | +3.3V_RUN |

| 2                              | +3.3V_RUN  | 14  |           |

| 3                              | GND        | 15  | GND       |

| 4                              | +5V_RUN    | 16  | PS_ON#    |

| 5                              | GND        | 17  | GND       |

| 6                              | +5V_RUN    | 18  | GND       |

| 7                              | GND        | 19  | GND       |

| 8                              | PWR_OK_ATX | 20  |           |

| 9                              | +5V_ALW    | 21  | +5V_RUN   |

| 10                             | +12V_RUN   | 22  | +5V_RUN   |

| 11                             | +12V_RUN   | 23  | +5V_RUN   |

| 12                             | +3.3V_RUN  | 24  | GND       |

Auxiliary Power Connector – CN7

Pin

5

6

7

Signal

GND

GND

GND

Power Connector CN10 is type Molex Mini-Fit Jr. connector, p/n 39-28-1243, or equivalent, with the pin-out indicated in the table here on the left (it is the standard 24-pin ATX pin-out).

Mating Connector, MOLEX p/n 39-01-2240 or equivalent, with female crimp terminal MOLEX series 5566.

PS\_ON#: this signal is present only if the board is configured, via CN11 and J2, to work in ATX mode. If working in AT mode, this pin is connected directly to Ground.

Power connector can be set to work in ATX mode or AT mode by using dedicated jumpers CN11 and J2, which are a standard pin headers, P2.54mm, 1x3 pin.

| CN11 position | J2 position | Power mode |

|---------------|-------------|------------|

| 2-3           | Not Care    | AT mode    |

| 1-2           | 1-2         | ATX mode   |

| 1-2           | 2-3         | AT mode    |

The board has an Auxiliary Power connector CN7 providing +12V\_RUN for the carrier board section only, in case multiple PCI-e modules are connected.

CN7 is 6-poles connector, type MOLEX mini-Fit Jr. p/n 39-28-1063 or equivalent.

Mating Connector, MOLEX p/n 39-01-2060 or equivalent, with female crimp terminal MOLEX series 5566.

| PINT  | Pins |

|-------|------|

| Pin 4 | Pin  |

|       |      |

|       |      |

|       |      |

|       |      |

Pin Signal

1

2

3

+12V RUN

+12V RUN

+12V RUN

| CPU Power Connector – CN8 |        |     |          |

|---------------------------|--------|-----|----------|

| Pin                       | Signal | Pin | Signal   |

| 1                         | GND    | 5   | +12V_RUN |

| 2                         | GND    | 6   | +12V_RUN |

| 3                         | GND    | 7   | +12V_RUN |

| 4                         | GND    | 8   | +12V_RUN |

The board has a CPU Power Connector CN8 providing  $+12V_RUN$  for the COM Express<sup>TM</sup> module only.

CN8 is a Molex Mini-Fit jr. 8 poles connector, p/n 39-28-1083 or equivalent.

Mating Connector, MOLEX p/n 39-01-2080 or equivalent, with female crimp terminal MOLEX series 5566.

| Pin 1<br>Pin 5 | Pin 4<br>Pin 8 |

|----------------|----------------|

|                |                |

The use of wires with section 18 AWG is recommended, in order to ensure the proper amperage of the power section.

| JP2 position | +5V_ALW Current monitor selector |

|--------------|----------------------------------|

| Not inserted | Current measurement enabled      |

| Inserted     | Current measurement disabled     |

The power consumption on +5V\_ALW can be monitored by removing 2 way jumper JP2 and inserting a tester set as ammeter.

Alternatively, the consumption on  $+5V_{ALW}$  can be monitored by inserting a tester set as ammeter between pin 1 and 2 of  $+5V_{ALW}$  Sense Connector CN4.

CN4 is a dedicated 2 position Wire to Board Terminal Block, type Wurth p/n 691210910002.

| CN3 position | Power Ok management |

|--------------|---------------------|

| 1-2          | PSU PWR_OK enabled  |

| 2-3          | PWR_OK always high  |

The COM Express<sup>™</sup> card edge connector has a PWR\_OK signal from main power supplied by Carrier Board to the module, indicating that all the power supplies to the Module are stable within specified ranges. The Module will typically not power up until the PWR\_OK signal goes active.

2-3 PWR\_OK always high CN3 is a standard pin header, P2.54mm, 1x3 pin, dedicated to manage this power 1003 status signal for the Module. For normal operation, set the jumper in 1-2 position, otherwise set in 2-3 position to fix its level high and have it always activated.

Diode LED D17 is present on Carrier Board to notify the system has been correctly powered-up, directly driven through an High-Speed Buffer by PWR\_OK signal.

Another diode LED D16, complementary to D17, is used to notify the Reset Output from Module to Carrier Board, directly driven through an High-Speed Buffer by CB\_RESET# signal.

#### 2.3.1 Smart Battery SM Bus Connector

| Smart Battery SM Bus Connector – CN29 |            |     |            |  |  |  |  |

|---------------------------------------|------------|-----|------------|--|--|--|--|

| Pin                                   | Signal     | Pin | Signal     |  |  |  |  |

| 1                                     | SB_SMB_CLK | 3   | SMB_ALERT# |  |  |  |  |

| 2                                     | SB_SMB_DAT | 4   | GND        |  |  |  |  |

The SM bus coming from COM Express<sup>M</sup> module is carried directly both to the Feature header (see par.3.3.8) and to a JST 4-pin connector CN29, p/n B4B-PH-K-S(LF)(SN), or equivalent, which can be used for the connection of external Smart battery controllers. Pinout as indicated in the left table.

SB\_SMB\_CLK: Smart Battery System Management bus bidirectional clock line, +3.3V\_ALW electrical level with 10k $\Omega$  pull up resistor derived by SMB\_CK signal

SB\_SMB\_DAT: Smart Battery System Management bus bidirectional data line, +3.3V\_ALW electrical level with 10k0 pull up resistor derived by SMB\_DAT signal

SMB\_ALERT#: System Management Bus Alert, active low input to the module that can be used to generate an Interrupt or to wake the system.

#### 2.3.2 RTC Battery

For the occurrences when the System (Carrier board + COM Express<sup>™</sup> module) is not powered with an external power supply, on board there is a RTC Coin Cell Battery holder CN9, for the use of standard coin battery type CR2032 with a nominal capacity of 220mAh, to supply, with a 3V voltage, the Real Time Clock and CMOS memory mounted on the COM Express<sup>™</sup> module.

The batteries should only be replaced with devices of the same type. Always check the orientation before inserting and make sure that they are aligned correctly and are not damaged or leaking.

#### CAUTION: handling batteries incorrectly or replacing with not-approved devices may present a risk of fire or explosion.

Never allow the batteries to become short-circuited during handling. Batteries supplied with C96 board are compliant to requirements of European Directive 2006/66/EC regarding batteries and accumulators. When putting out of order C96 board, remove the batteries from the board in order to collect and dispose them according to the requirement of the same European Directive above mentioned. Even when replacing the batteries, the disposal has to be made according to these requirements.

| CN6 position | RTC Battery enable   | It is possible to monitor the consumption on VCC_RTC battery by removing the jumper from CN6 connector and inserting a tester in series set as ammeter between 2-3 position. |

|--------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-2          | Battery disconnected | Alternatively, the consumption on VCC_RTC can be monitored by inserting a tester set as ammeter                                                                              |

| 2-3          | Battery connected    | between pin 1 and 2 of RTC Battery Sense Connector CN5.                                                                                                                      |

| NO jumper    | Current measurement  | CN5 is a dedicated 2 position Wire to Board Terminal Block, type Wurth p/n 691210910002                                                                                      |

RTC battery can be enabled/disabled using dedicated jumper on CN6, which is a standard pin header, P2.54mm, 1x3 pin.

CCOME-C96 CCOMe-C96 - Rev. First Edition: 1.0 - Last Edition: 1.0 - Author: A.R. - Reviewed by C.M. Copyright © 2021 SECO S.p.A.

| JP1 posit   | ion Battery Low Indicator enable | The RTC battery voltage level is monitored through a comparator inside the board. Battery |

|-------------|----------------------------------|-------------------------------------------------------------------------------------------|

| Not inserte | ed Indicator disabled            | low status signal (BATLOW#) is carried to COM-express <sup>™</sup> module to be managed.  |

| Inserted    | Indicator enabled                | JP1 is a 2-way jumper to enable/disable this indicator.                                   |

#### 2.3.3 Power Rails meanings

In all the tables contained in this manual, Power rails are named with the following meaning:

\_RUN: Switched voltages, i.e. power rails that are active only when the board is in ACPI's S0 (Working) state. Examples: +3.3V\_RUN, +5V\_RUN.

\_ALW: Always-on voltages, i.e. power rails that are active both in ACPI's S0 (Working), S3 (Standby) and S5 (Soft Off) state. Examples: +5V\_ALW, +3.3V\_ALW.

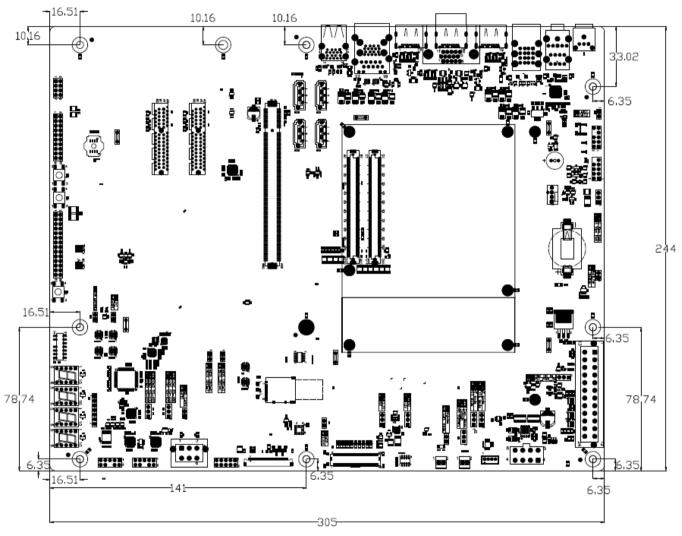

## 2.4 Mechanical Specifications

According to ATX form factor, board dimensions are 305 x 244 mm (12" x 9.6").

The printed circuit of the board is made of twelve layers, some of them are ground planes, for disturbance rejection.

In order to fix the COM Express<sup>™</sup> module to the carrier board, on CCOMe-C96 have been soldered six metallic spacers, height 8mm, 2.5mm diameter.

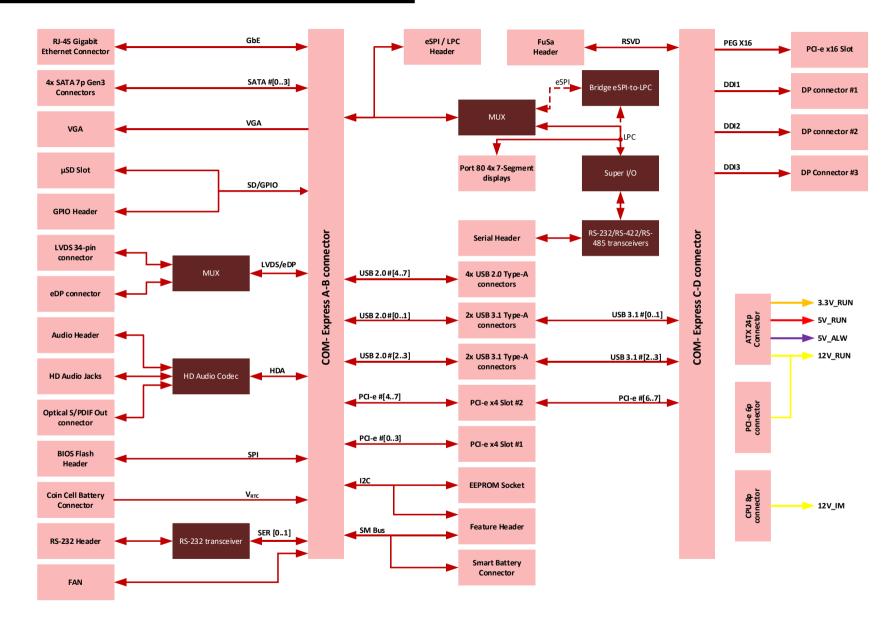

## 2.5 Block Diagram

## Chapter 3. CONNECTORS

- Connectors placement

- Connectors overview

- Connectors description

## 3.1 Connectors placement

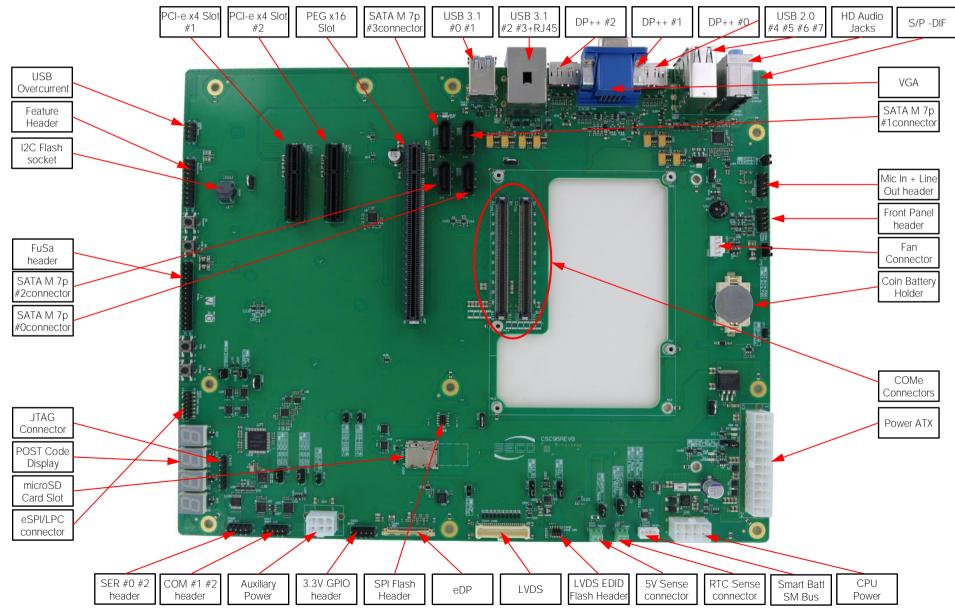

On CCOMe-C96 carrier board, there are several connectors. Some of them are standard connectors, like Display Port, Gigabit Ethernet, USB ports, and are placed on the same side of the board, so that they can be placed on a panel of a possible enclosure.

In the following picture it is possible to see the position of each connector.

## 3.2 Connectors overview

#### 3.2.1 Connectors list

| Name | Description                                                   | Name | Description                           |

|------|---------------------------------------------------------------|------|---------------------------------------|

| CN1  | Com Express <sup>™</sup> , A-B rows Connector                 | CN28 | External BIOS SPI Flash Header        |

| CN2  | Com Express <sup>™</sup> , C-D rows Connector                 | CN29 | Smart Battery SM Bus Connector        |

| CN4  | +5V_ALW Sense Connector                                       | CN30 | VGA Connector                         |

| CN5  | RTC Battery Sense Connector                                   | CN31 | GPIO pin Header                       |

| CN7  | Auxiliary Power Connector                                     | CN32 | FAN Connector                         |

| CN8  | CPU Power Connector                                           | CN33 | microSD Card Slot                     |

| CN9  | RTC Coin Cell Battery Connector                               | CN34 | Front Panel Header                    |

| CN10 | Power ATX Connector                                           | CN35 | External EEPROM I2C Flash socket      |

| CN12 | PCI-e x4 slot #1                                              | CN36 | HD Audio Jacks                        |

| CN13 | PCI-e Graphics (PEG) x16 slot                                 | CN38 | Mic In + Line Out internal pin Header |

| CN14 | PCI-e x4 slot #2                                              | CN42 | eDP Connector                         |

| CN15 | eSPI/LPC Debug Connector                                      | CN44 | LVDS Connector                        |

| CN16 | JTAG Connector                                                | CN45 | LVDS External EDID Flash Header       |

| CN17 | COM ports Internal pin Header                                 | CN52 | DP++ #0 Connector                     |

| CN18 | USB 3.1 ports #0 #1 Dual Type-A socket                        | CN53 | DP++ #1 Connector                     |

| CN19 | Combo USB 3.1 ports #2 #3 Dual Type-A socket + RJ45 Connector | CN54 | DP++ #2 Connector                     |

| CN20 | USB 2.0 ports #4 #5 #6 #7 Quad Type-A socket                  | CN55 | USB Overcurrent Header                |

| CN21 | SATA M 7-p #2 Connector                                       | CN56 | S/P-DIF Out Connector                 |

| CN22 | SATA M 7-p #3 Connector                                       | J1   | FuSa Header                           |

| CN24 | SATA M 7-p #0 Connector                                       |      |                                       |

| CN25 | SATA M 7-p #1 Connector                                       |      |                                       |

| CN26 | RS-232 ports Internal pin Header                              |      |                                       |

| CN27 | Feature pin Header                                            |      |                                       |

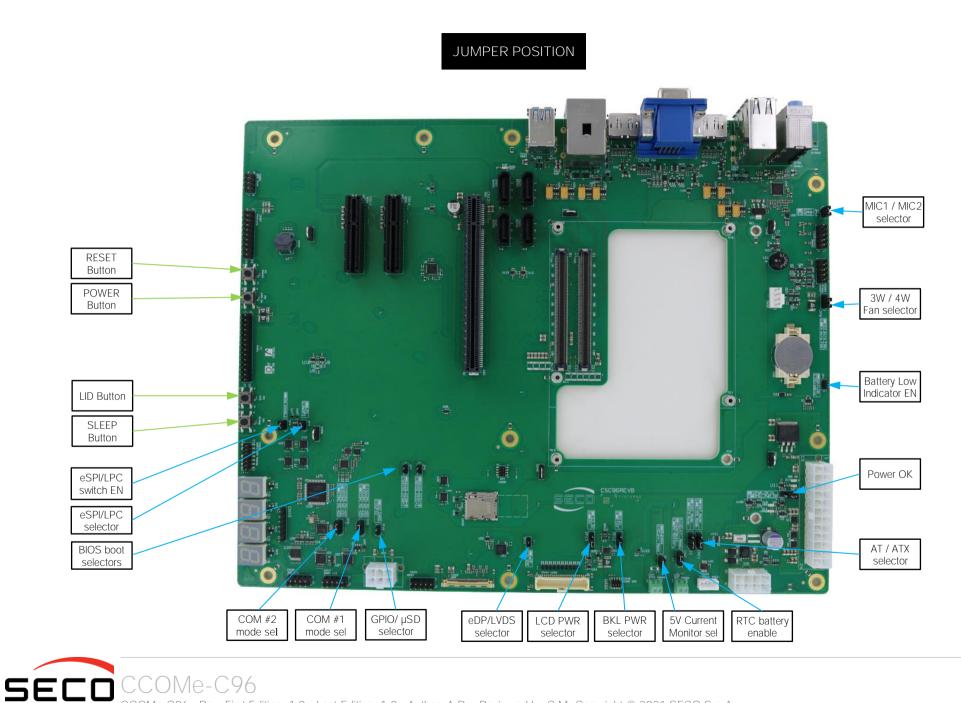

#### 3.2.2 Jumpers and switch list

| Name      | Description                      |

|-----------|----------------------------------|

| CN3       | Power OK management              |

| CN6       | RTC Battery enable               |

| CN11 / J2 | AT/ATX mode selectors            |

| JP1       | RTC Battery Low Indicator enable |

| JP2       | +5V_ALW Current monitor selector |

| JP3       | eSPI/LPC selector                |

| JP4       | eSPI/LPC switch enable           |

| JP5       | COM 1 mode selector              |

| JP6       | COM 2 mode selector              |

| JP7 / JP8 | BIOS Boot selectors              |

| JP9       | FAN driver mode selector         |

| JP10      | GPIO/SD Card selector            |

| JP11      | eDP/LVDS selector                |

| JP12      | Backlight Power selector         |

| JP13      | LCD Power selector               |

| JP14      | MIC1 / MIC2 selector             |

## 3.3 Connectors description

CCOMe-C96

#### 3.3.1 COM Express<sup>™</sup> module connectors

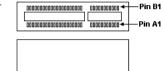

For the connection of COM Express<sup>™</sup> CPU modules, on board there are two connectors, type TYCO 3-6318491-6 (220 pin dual row plug, ultra thin, 0.5mm pitch, h=8mm), as requested by COM Express<sup>™</sup> specifications.

The pinout of these connectors will be briefly described in the following paragraphs. Please refer to COM Express<sup>™</sup> standard for a better description of each signal.

| COM Express <sup>™</sup> Connector CN1 - Rows A & B |                |         |         |                          |                                                               |  |  |

|-----------------------------------------------------|----------------|---------|---------|--------------------------|---------------------------------------------------------------|--|--|

| Description                                         | Pin name       | Pin nr. | Pin nr. | Pin name                 | Description                                                   |  |  |

| Power Ground                                        | GND            | A1      | B1      | GND                      | Power Ground                                                  |  |  |

| GbEthernet Differential pair 3-                     | GBE0_MDI3-     | A2      | B2      | GBE0_ACT#                | GbEth Activity indicator                                      |  |  |

| GbEthernet Differential pair 3+                     | GBE0_MDI3+     | A3      | B3      | LPC_FRAME# / ESPI_CS0#   | LPC Frame Indicator / eSPI Chip Select                        |  |  |

| GbEthernet 100Mb/s link ind.                        | GBE0_LINK100#  | A4      | B4      | LPC_AD0 / ESPI_IO_0      | LPC Address / Data Bus 0<br>eSPI Master Data Input / Output 0 |  |  |

| GbEthernet 1000Mb/s link ind.                       | GBE0_LINK1000# | A5      | B5      | LPC_AD1 / ESPI_IO_1      | LPC Address / Data Bus 1<br>eSPI Master Data Input / Output 1 |  |  |

| GbEthernet differential pair 2-                     | GBE0_MDI2-     | A6      | B6      | LPC_AD2 / ESPI_IO_2      | LPC Address / Data Bus 2<br>eSPI Master Data Input / Output 2 |  |  |

| GbEthernet Differential pair 2+                     | GBE0_MDI2+     | A7      | B7      | LPC_AD3 / ESPI_IO_3      | LPC Address / Data Bus 3<br>eSPI Master Data Input / Output 3 |  |  |

| Not connected                                       | N.C.           | A8      | B8      | LPC_DRQ0# / ESPI_ALERT0# | LPC serial DMA request<br>eSPI Alert request service signal   |  |  |

| GbEthernet Differential pair 1-                     | GBE0_MDI1-     | A9      | B9      | N.C.                     | Not connected                                                 |  |  |

| GbEthernet Differential pair 1+                     | GBE0_MDI1+     | A10     | B10     | LPC_CLK / ESPI_CK        | LPC Clock Output 33MHz<br>eSPI Master Clock Output            |  |  |

| Power Ground                                        | GND            | A11     | B11     | GND                      | Power Ground                                                  |  |  |

| GbEthernet Differential pair 0-                     | GBE0_MDIO-     | A12     | B12     | PWRBTN#                  | Power Button                                                  |  |  |

| GbEthernet Differential pair 0+                     | GBE0_MDI0+     | A13     | B13     | SMB_CK                   | SM Bus Clock                                                  |  |  |

| GbEthernet Reference Voltage                        | GBE0_CTREF     | A14     | B14     | SMB_DAT                  | SM Bus Data                                                   |  |  |

| Suspend to RAM (S3) signal                          | SUS_S3#        | A15     | B15     | SMB_ALERT#               | SM Bus Alert signal                                           |  |  |

| SATAO Transmit Data +                    | SATA0_TX+     | A16 | B16 | SATA1_TX+               | SATA1 Transmit Data +                    |

|------------------------------------------|---------------|-----|-----|-------------------------|------------------------------------------|

| SATAO Transmit Data -                    | SATAO_TX-     | A17 | B17 | SATA1_TX-               | SATA1 Transmit Data -                    |

| Suspend to Disk (S4) signal              | SUS_S4#       | A18 | B18 | SUS_STAT# / ESPI_RESET# | LPC Suspend Mode Indicator<br>eSPI Reset |

| SATAO Receive Data +                     | SATAO_RX+     | A19 | B19 | SATA1_RX+               | SATA1 Receive Data +                     |

| SATAO Receive Data -                     | SATAO_RX-     | A20 | B20 | SATA1_RX-               | SATA1 Receive Data -                     |

| Power Ground                             | GND           | A21 | B21 | GND                     | Power Ground                             |

| SATA2 Transmit Data +                    | SATA2_TX+     | A22 | B22 | SATA3_TX+               | SATA3 Transmit Data +                    |

| SATA2 Transmit Data -                    | SATA2_TX-     | A23 | B23 | SATA3_TX-               | SATA3 Transmit Data -                    |

| Soft Off (S5) Signal                     | SUS_S5#       | A24 | B24 | PWR_OK                  | Power OK signal                          |

| SATA2 Receive Data +                     | SATA2_RX+     | A25 | B25 | SATA3_RX+               | SATA3 Receive Data +                     |

| SATA2 Receive Data -                     | SATA2_RX-     | A26 | B26 | SATA3_RX-               | SATA3 Receive Data -                     |

| Low Battery Status Indicator Input       | BATLOW#       | A27 | B27 | WDT                     | Watchdog Event indicator Output          |

| SATA LED                                 | SATA_ACT#     | A28 | B28 | N.C.                    | Not connected                            |

| HD Audio Sync signal                     | AC/HDA_SYNC   | A29 | B29 | N.C.                    | Not Connected                            |

| HD Audio Reset                           | AC/HDA_RST#   | A30 | B30 | HDA_SDIN0               | HD Audio Serial TDM Input 0              |

| Power Ground                             | GND           | A31 | B31 | GND                     | Power Ground                             |

| HD Audio Bit Clock                       | AC/HDA_BITCLK | A32 | B32 | SPKR                    | Speaker                                  |

| HD Audio Serial TDM Output               | AC/HDA_SDOUT  | A33 | B33 | I2C_CK                  | I2C Clock                                |

| BIOS boot device select 0 signal         | BIOS_DISO#    | A34 | B34 | I2C_DAT                 | I2C Data                                 |

| Thermal shutdown Status Indicator Output | THRMTRIP#     | A35 | B35 | THRM#                   | Thermal Alarm Input                      |

| USB Data Port 6 -                        | USB6-         | A36 | B36 | USB7-                   | USB Data Port 7-                         |

| USB Data Port 6 +                        | USB6+         | A37 | B37 | USB7+                   | USB Data Port 7+                         |

| USB Over Current Ports 6/7               | USB_6_7_OC#   | A38 | B38 | USB_4_5_OC#             | USB Over Current Ports 4/5               |

| USB Data Port 4 -                        | USB4-         | A39 | B39 | USB5-                   | USB Data Port 5-                         |

| USB Data Port 4 +                        | USB4+         | A40 | B40 | USB5+                   | USB Data Port 5+                         |

| Power Ground                             | GND           | A41 | B41 | GND                     | Power Ground                             |

| USB Data Port 2 -                        | USB2-         | A42 | B42 | USB3-                   | USB Data Port 3-                         |

| USB Data Port 2 +                        | USB2+         | A43 | B43 | USB3+                   | USB Data Port 3+                         |

| USB Over Current Ports 2/3               | USB_2_3_OC#   | A44 | B44 | USB_0_1_OC#             | USB Over Current Ports 0/1               |

|                                          |               |     |     |                         |                                          |

| USB Data Port 0 -                     | USB0-             | A45 | B45 | USB1-        | USB Data Port 1-               |

|---------------------------------------|-------------------|-----|-----|--------------|--------------------------------|

| USB Data Port 0 +                     | USB0+             | A46 | B46 | USB1+        | USB Data Port 1+               |

| Real Time Clock power line            | VCC_RTC           | A47 | B47 | EXCD1_PERST# | eSPI enable Input              |

| Not Connected                         | N.C.              | A48 | B48 | N.C.         | Not Connected                  |

| Not Connected                         | N.C.              | A49 | B49 | SYS_RESET#   | Reset Button Input             |

| LPC serial interrupt request          | LPC_SERIRQ        | A50 | B50 | CB_RESET#    | Board Reset Output             |

| Power Ground                          | GND               | A51 | B51 | GND          | Power Ground                   |

| PCI-E lane 5 transmit +               | PCIE_TX5+         | A52 | B52 | PCIE_RX5+    | PCI-E lane 5 receive +         |

| PCI-E lane 5 transmit -               | PCIE_TX5-         | A53 | B53 | PCIE_RX5-    | PCI-E lane 5 receive -         |

| GP Input 0 / SDIO data signal 0       | GPIO/SD_DATAO     | A54 | B54 | GPO1/SD_CMD  | GP Output 1 / SDIO CMD output  |

| PCI-E lane 4 transmit +               | PCIE_TX4+         | A55 | B55 | PCIE_RX4+    | PCI-E lane 4 receive +         |

| PCI-E lane 4 transmit -               | PCIE_TX4-         | A56 | B56 | PCIE_RX4-    | PCI-E lane 4 receive -         |

| Power Ground                          | GND               | A57 | B57 | GPO2/SD_WP   | GP Output 2 / SDIO WP input    |

| PCI-E lane 3 transmit +               | PCIE_TX3+         | A58 | B58 | PCIE_RX3+    | PCI-E lane 3 receive +         |

| PCI-E lane 3 transmit -               | PCIE_TX3-         | A59 | B59 | PCIE_RX3-    | PCI-E lane 3 receive -         |

| Power Ground                          | GND               | A60 | B60 | GND          | Power Ground                   |

| PCI-E lane 2 transmit +               | PCIE_TX2+         | A61 | B61 | PCIE_RX2+    | PCI-E lane 2 receive +         |

| PCI-E lane 2 transmit -               | PCIE_TX2-         | A62 | B62 | PCIE_RX2-    | PCI-E lane 2 receive -         |

| GP Input 1 / SDIO data signal 1       | GPI1/SD_DATA1     | A63 | B63 | GPO3/SD_CD#  | GP Output 3 / SDIO CD# input   |

| PCI-E lane 1 transmit +               | PCIE_TX1+         | A64 | B64 | PCIE_RX1+    | PCI-E lane 1 receive +         |

| PCI-E lane 1 transmit -               | PCIE_TX1-         | A65 | B65 | PCIE_RX1-    | PCI-E lane 1 receive -         |

| Power Ground                          | GND               | A66 | B66 | WAKEO#       | PCI-express wake up signal     |

| GP Input 2 / SDIO data signal 2       | GPI2/SD_DATA2     | A67 | B67 | WAKE1#       | General purpose wake up signal |

| PCI-E lane 0 transmit +               | PCIE_TX0+         | A68 | B68 | PCIE_RX0+    | PCI-E lane 0 receive +         |

| PCI-E lane 0 transmit -               | PCIE_TX0-         | A69 | B69 | PCIE_RX0-    | PCI-E lane 0 receive -         |

| Power Ground                          | GND               | A70 | B70 | GND          | Power Ground                   |

| LVDS Ch. A Data 0 + / eDP Ch. Data 2+ | LVDS_A0+/eDP_TX2+ | A71 | B71 | LVDS_B0+     | LVDS Ch. B Data 0 +            |

| LVDS Ch. A Data 0 - / eDP Ch. Data 2- | LVDS_A0-/eDP_TX2- | A72 | B72 | LVDS_B0-     | LVDS Ch. B Data 0 -            |

| LVDS Ch. A Data 1+ / eDP Ch. Data 1+  | LVDS_A1+/eDP_TX1+ | A73 | B73 | LVDS_B1+     | LVDS Ch. B Data 1 +            |

| LVDS Ch. A Data 1- / eDP Ch. Data 1-  | LVDS_A1-/eDP_TX1- | A74 | B74 | LVDS_B1-     | LVDS Ch. B Data 1 -            |

|                                       |                   |     |     |              |                                |

| LVDS Ch. A Data 2+ / eDP Ch. Data 0+                                             | LVDS_A2+/eDP_TX0+     | A75  | B75  | LVDS_B2+       | LVDS Ch. B Data 2 +              |

|----------------------------------------------------------------------------------|-----------------------|------|------|----------------|----------------------------------|

| LVDS Ch. A Data 2- / eDP Ch. Data 0-                                             | LVDS_A2-/eDP_TX0+     | A76  | B76  | LVDS_B2-       | LVDS Ch. B Data 2 -              |

| LVDS Panel Power Enable                                                          | LVDS_VDD_EN           | A77  | B77  | LVDS_B3+       | LVDS Ch. B Data 3 +              |

| LVDS Ch. A Data 3 +                                                              | LVDS_A3+              | A78  | B78  | LVDS_B3-       | LVDS Ch. B Data 3 -              |

| LVDS Ch. A Data 3 -                                                              | LVDS_A3-              | A79  | B79  | LVDS_BKLT_EN   | LVDS Panel Backlight ON          |

| Power Ground                                                                     | GND                   | A80  | B80  | GND            | Power Ground                     |

| LVDS Ch. A Clock + / eDP Ch. Data 3+                                             | LVDS_A_CK+/eDP_TX3+   | A81  | B81  | LVDS_B_CK+     | LVDS Ch. B Clock +               |

| LVDS Ch. A Clock - / eDP Ch. Data 3-                                             | LVDS_A_CK-/eDP_TX3-   | A82  | B82  | LVDS_B_CK-     | LVDS Ch. B Clock -               |

| LVDS I2C Clock / eDP Ch. Aux +                                                   | LVDS_I2C_CK/eDP_AUX+  | A83  | B83  | LVDS_BKLT_CTRL | LVDS Backlight Brightness        |

| LVDS I2C Data / eDP Ch. Aux -                                                    | LVDS_I2C_DAT/eDP_AUX- | A84  | B84  | +5V_A          | +5V Standby power line           |

| GP Input 3 / SDIO data signal 3                                                  | GPI3/SD_DATA3         | A85  | B85  | +5V_A          | +5V Standby power line           |

| Not Connected                                                                    | RSVD                  | A86  | B86  | +5V_A          | +5V Standby power line           |

| eDP Hot Plug Detect Signal                                                       | eDP_HPD               | A87  | B87  | +5V_A          | +5V Standby power line           |

| PCI-E Clock reference +                                                          | PCIE_CK_REF+          | A88  | B88  | BIOS_DIS1#     | BIOS boot device select 1 signal |

| PCI-E Clock reference -                                                          | PCIE_CK_REF-          | A89  | B89  | VGA_RED        | VGA Red for monitor Output       |

| Power Ground                                                                     | GND                   | A90  | B90  | GND            | Power Ground                     |

| Power supply for Carrier Board SPI Device                                        | SPI_POWER             | A91  | B91  | VGA_GRN        | VGA Green for monitor Output     |

| Data in to Module from Carrier SPI Device                                        | SPI_MISO              | A92  | B92  | VGA_BLU        | VGA Blu for monitor Output       |

| GP Output 0 / SDIO Clock                                                         | GPO0 / SD_CLK         | A93  | B93  | VGA_HSYNC      | VGA Horizontal sync output       |

| Clock from Module to Carrier SPI Device                                          | SPI_CLK               | A94  | B94  | VGA_VSYNC      | VGA Vertical sync output         |

| Data out from Module to carrier SPI device                                       | SPI_MOSI              | A95  | B95  | VGA_I2C_CK     | DDC clock line                   |

| TPM Physical Presence pin, Active High<br>Input for optional on-board TPM device | TPM_PP                | A96  | B96  | VGA_I2C_DAT    | DDC data line                    |

| Type10 signal: Not connected                                                     | Type10#               | A97  | B97  | SPI_CS#        | SPI Chip Select signal           |

| Module's serial port 0 TX                                                        | SER0_TX               | A98  | B98  | RSVD           | Not Connected                    |

| Module's serial port 0 RX                                                        | SER0_RX               | A99  | B99  | RSVD           | Not Connected                    |

| Power Ground                                                                     | GND                   | A100 | B100 | GND            | Power Ground                     |

| Module's serial port 1 TX                                                        | SER1_TX               | A101 | B101 | FAN_PWMOUT     | FAN Speed control                |

| Module's serial port 1 RX                                                        | SER1_RX               | A102 | B102 | FAN_TACHIN     | FAN tachometer input             |

| LID button input                                                                 | LID#                  | A103 | B103 | SLEEP#         | Sleep Button Input               |

| +12V switched power supply                                                       | +12V_S                | A104 | B104 | +12V_S         | +12V switched power supply       |

|                                                                                  |                       |      |      |                |                                  |

| +12V switched power supply     | +12V_S     | A105                      | B105    | +12V_S             | +12V switched power supply      |

|--------------------------------|------------|---------------------------|---------|--------------------|---------------------------------|

| +12V switched power supply     | +12V_S     | A106                      | B106    | +12V_S             | +12V switched power supply      |

| +12V switched power supply     | +12V_S     | A107                      | B107    | +12V_S             | +12V switched power supply      |

| +12V switched power supply     | +12V_S     | A108                      | B108    | +12V_S             | +12V switched power supply      |

| +12V switched power supply     | +12V_S     | A109                      | B109    | +12V_S             | +12V switched power supply      |

| Power Ground                   | GND        | A110                      | B110    | GND                | Power Ground                    |

|                                | COM Ex     | press <sup>™</sup> Conneo | ctor CN | 3 - Rows C & D     |                                 |

| Description                    | Pin name   | Pin nr.                   | Pin nr. | Pin name           | Description                     |

| Power Ground                   | GND        | C1                        | D1      | GND                | Power Ground                    |

| Power Ground                   | GND        | C2                        | D2      | GND                | Power Ground                    |

| SuperSpeed USB receive pair 0- | USB_SSRX0- | С3                        | D3      | USB_SSTX0-         | SuperSpeed USB transmit pair 0- |

| SuperSpeed USB receive pair 0+ | USB_SSRX0+ | C4                        | D4      | USB_SSTX0+         | SuperSpeed USB transmit pair 0+ |

| Power ground                   | GND        | C5                        | D5      | GND                | Power ground                    |

| SuperSpeed USB receive pair 1- | USB_SSRX1- | C6                        | D6      | USB_SSTX1-         | SuperSpeed USB transmit pair 1- |

| SuperSpeed USB receive pair 1+ | USB_SSRX1+ | C7                        | D7      | USB_SSTX1+         | SuperSpeed USB transmit pair 1+ |

| Power ground                   | GND        | C8                        | D8      | GND                | Power ground                    |

| SuperSpeed USB receive pair 2- | USB_SSRX2- | С9                        | D9      | USB_SSTX2-         | SuperSpeed USB transmit pair 2- |

| SuperSpeed USB receive pair 2+ | USB_SSRX2+ | C10                       | D10     | USB_SSTX2+         | SuperSpeed USB transmit pair 2+ |

| Power Ground                   | GND        | C11                       | D11     | GND                | Power Ground                    |

| SuperSpeed USB receive pair 3- | USB_SSRX3- | C12                       | D12     | USB_SSTX3-         | SuperSpeed USB transmit pair 3- |

| SuperSpeed USB receive pair 3+ | USB_SSRX3+ | C13                       | D13     | USB_SSTX3+         | SuperSpeed USB transmit pair 3+ |

| Power Ground                   | GND        | C14                       | D14     | GND                | Power Ground                    |

| Not Connected                  | N.C.       | C15                       | D15     | DDI1_CTRLCLK_AUX+  | DP1 Aux+ or TMDS1 I2C_CLK       |

| Not Connected                  | N.C.       | C16                       | D16     | DDI1_CTRLDATA_AUX- | DP1 Aux- or TMDS1 I2C_DAT       |

| Reserved Purpose Signal        | RSVD#C17   | C17                       | D17     | RSVD#D17           | Reserved Purpose Signal         |

| Reserved Purpose Signal        | RSVD#C18   | C18                       | D18     | RSVD#D18           | Reserved Purpose Signal         |

| PCI Express Receive Pair 6+    | PCIE_RX6+  | C19                       | D19     | PCIE_TX6+          | PCI Express Transmit Pair 6+    |

| PCI Express Receive Pair 6-    | PCIE_RX6-  | C20                       | D20     | PCIE_TX6-          | PCI Express Transmit Pair 6-    |

| Power Ground                   | GND        | C21                       | D21     | GND                | Power Ground                    |

| PCI Express Receive Pair 7+    | PCIE_RX7+  | C22                       | D22     | PCIE_TX7+          | PCI Express Transmit Pair 7+    |

|                                |            |                           |         |                    |                                 |

SECOME-C96 CCOME-C96 - Rev. First Edition: 1.0 - Last Edition: 1.0 - Author: A.R. - Reviewed by C.M. Copyright © 2021 SECO S.p.A.

| PCI Express Receive Pair 7-                 | PCIE_RX7-          | C23 | D23 | PCIE_TX7-        | PCI Express Transmit Pair 7-                |

|---------------------------------------------|--------------------|-----|-----|------------------|---------------------------------------------|

| Digital Display Interface 1 Hot-Plug Detect | DDI1_HPD           | C24 | D24 | RSVD#D24         | Reserved Purpose Signal                     |

| Not Connected                               | N.C.               | C25 | D25 | RSVD#D25         | Reserved Purpose Signal                     |

| Not Connected                               | N.C.               | C26 | D26 | DDI1_PAIR0+      | Digital Display interface 1 pair 0+         |

| Reserved Purpose Signal                     | RSVD#C27           | C27 | D27 | DDI1_PAIR0-      | Digital Display interface 1 pair 0-         |

| Reserved Purpose Signal                     | RSVD#C28           | C28 | D28 | RSVD#D28         | Reserved Purpose Signal                     |

| Not Connected                               | N.C.               | C29 | D29 | DDI1_PAIR1+      | Digital Display interface 1 pair 1+         |

| Not Connected                               | N.C.               | C30 | D30 | DDI1_PAIR1-      | Digital Display interface 1 pair 1-         |

| Power Ground                                | GND                | C31 | D31 | GND              | Power Ground                                |

| DP2 Aux+ or TMDS2 I2C_CLK                   | DDI2_CTRLCLK_AUX+  | C32 | D32 | DDI1_PAIR2+      | Digital Display interface 1 pair 2+         |

| DP2 Aux- or TMDS2 I2C_DAT                   | DDI2_CTRLDATA_AUX- | C33 | D33 | DDI1_PAIR2-      | Digital Display interface 1 pair 2-         |

| DP2 or TMDS2 selector                       | DDI2_DDC_AUX_SEL   | C34 | D34 | DDI1_DDC_AUX_SEL | DP1 or TMDS1 selector                       |

| Reserved Purpose Signal                     | RSVD#C35           | C35 | D35 | RSVD#D35         | Reserved Purpose Signal                     |

| DP3 Aux+ or TMDS3 I2C_CLK                   | DDI3_CTRLCLK_AUX+  | C36 | D36 | DDI1_PAIR3+      | Digital Display interface 1 pair 3+         |

| DP3 Aux- or TMDS3 I2C_DAT                   | DDI3_CTRLDATA_AUX- | C37 | D37 | DDI1_PAIR3-      | Digital Display interface 1 pair 3-         |

| DP3 or TMDS3 selector                       | DDI3_DDC_AUX_SEL   | C38 | D38 | RSVD#D38         | Reserved Purpose Signal                     |

| Digital Display interface 3 pair 0+         | DDI3_PAIR0+        | C39 | D39 | DDI2_PAIR0+      | Digital Display interface 2 pair 0+         |

| Digital Display interface 3 pair 0-         | DDI3_PAIRO-        | C40 | D40 | DDI2_PAIRO-      | Digital Display interface 2 pair 0-         |

| Power Ground                                | GND                | C41 | D41 | GND              | Power Ground                                |

| Digital Display interface 3 pair 1+         | DDI3_PAIR1+        | C42 | D42 | DDI2_PAIR1+      | Digital Display interface 2 pair 1+         |

| Digital Display interface 3 pair 1-         | DDI3_PAIR1-        | C43 | D43 | DDI2_PAIR1-      | Digital Display interface 2 pair 1-         |

| Digital Display Interface 3Hot-Plug Detect  | DDI3_HPD           | C44 | D44 | DDI2_HPD         | Digital Display Interface 2 Hot-Plug Detect |

| Reserved Purpose Signal                     | RSVD#C45           | C45 | D45 | RSVD#D45         | Reserved Purpose Signal                     |

| Digital Display interface 3 pair 2+         | DDI3_PAIR2+        | C46 | D46 | DDI2_PAIR2+      | Digital Display interface 2 pair 2+         |

| Digital Display interface 3 pair 2-         | DDI3_PAIR2-        | C47 | D47 | DDI2_PAIR2-      | Digital Display interface 2 pair 2-         |

| Reserved Purpose Signal                     | RSVD#C48           | C48 | D48 | RSVD#D48         | Reserved Purpose Signal                     |

| Digital Display interface 3 pair 3+         | DDI3_PAIR3+        | C49 | D49 | DDI2_PAIR3+      | Digital Display interface 2 pair 3+         |

| Digital Display interface 3 pair 3-         | DDI3_PAIR3-        | C50 | D50 | DDI2_PAIR3-      | Digital Display interface 2 pair 3-         |

| Power Ground                                | GND                | C51 | D51 | GND              | Power Ground                                |

| PCIe Graphics receive pair 0+               | PEG_RX0+           | C52 | D52 | PEG_TX0+         | PCIe Graphics transmit pair 0+              |

|                                             |                    |     |     |                  |                                             |

| PCIe Graphics receive pair 0- | PEG_RX0- | C53 | D53 | PEG_TX0- | PCIe Graphics transmit pair 0- |

|-------------------------------|----------|-----|-----|----------|--------------------------------|

| Type0 signal: Not Connected   | TYPEO#   | C54 | D54 | N.C.     | Not Connected                  |

| PCIe Graphics receive pair 1+ | PEG_RX1+ | C55 | D55 | PEG_TX1+ | PCIe Graphics transmit pair 1+ |

| PCIe Graphics receive pair 1- | PEG_RX1- | C56 | D56 | PEG_TX1- | PCIe Graphics transmit pair 1- |

| Type1 signal: Not Connected   | TYPE1#   | C57 | D57 | TYPE2#   | Type2 signal: +5V_A            |

| PCIe Graphics receive pair 2+ | PEG_RX2+ | C58 | D58 | PEG_TX2+ | PCIe Graphics transmit pair 2+ |

| PCle Graphics receive pair 2- | PEG_RX2- | C59 | D59 | PEG_TX2- | PCIe Graphics transmit pair 2- |

| Power Ground                  | GND      | C60 | D60 | GND      | Power Ground                   |

| PCle Graphics receive pair 3+ | PEG_RX3+ | C61 | D61 | PEG_TX3+ | PCIe Graphics transmit pair 3+ |

| PCIe Graphics receive pair 3- | PEG_RX3- | C62 | D62 | PEG_TX3- | PCIe Graphics transmit pair 3- |

| Reserved Purpose Signal       | RSVD#C63 | C63 | D63 | RSVD#D63 | Reserved Purpose Signal        |

| Reserved Purpose Signal       | RSVD#C64 | C64 | D64 | RSVD#D64 | Reserved Purpose Signal        |

| PCIe Graphics receive pair 4+ | PEG_RX4+ | C65 | D65 | PEG_TX4+ | PCIe Graphics transmit pair 4+ |

| PCle Graphics receive pair 4- | PEG_RX4- | C66 | D66 | PEG_TX4- | PCIe Graphics transmit pair 4- |

| Not Connected                 | RSVD#C67 | C67 | D67 | GND      | Power Ground                   |

| PCle Graphics receive pair 5+ | PEG_RX5+ | C68 | D68 | PEG_TX5+ | PCIe Graphics transmit pair 5+ |

| PCle Graphics receive pair 5- | PEG_RX5- | C69 | D69 | PEG_TX5- | PCIe Graphics transmit pair 5- |

| Power Ground                  | GND      | C70 | D70 | GND      | Power Ground                   |

| PCle Graphics receive pair 6+ | PEG_RX6+ | C71 | D71 | PEG_TX6+ | PCIe Graphics transmit pair 6+ |

| PCle Graphics receive pair 6- | PEG_RX6- | C72 | D72 | PEG_TX6- | PCIe Graphics transmit pair 6- |

| Power Ground                  | GND      | C73 | D73 | GND      | Power Ground                   |

| PCle Graphics receive pair 7+ | PEG_RX7+ | C74 | D74 | PEG_TX7+ | PCIe Graphics transmit pair 7+ |

| PCle Graphics receive pair 7- | PEG_RX7- | C75 | D75 | PEG_TX7- | PCIe Graphics transmit pair 7- |

| Power Ground                  | GND      | C76 | D76 | GND      | Power Ground                   |

| Reserved Purpose Signal       | RSVD#C77 | C77 | D77 | RSVD#D77 | Not Connected                  |

| PCle Graphics receive pair 8+ | PEG_RX8+ | C78 | D78 | PEG_TX8+ | PCIe Graphics transmit pair 8+ |

| PCle Graphics receive pair 8- | PEG_RX8- | C79 | D79 | PEG_TX8- | PCIe Graphics transmit pair 8- |

| Power Ground                  | GND      | C80 | D80 | GND      | Power Ground                   |

| PCle Graphics receive pair 9+ | PEG_RX9+ | C81 | D81 | PEG_TX9+ | PCIe Graphics transmit pair 9+ |

| PCle Graphics receive pair 9- | PEG_RX9- | C82 | D82 | PEG_TX9- | PCIe Graphics transmit pair 9- |

|                               |          |     |     |          |                                |

| Not Connected                  | RSVD#C83  | C83  | D83  | RSVD#D83  | Not Connected                   |

|--------------------------------|-----------|------|------|-----------|---------------------------------|

| Power Ground                   | GND       | C84  | D84  | GND       | Power Ground                    |

| PCle Graphics receive pair 10+ | PEG_RX10+ | C85  | D85  | PEG_TX10+ | PCIe Graphics transmit pair 10+ |

| PCIe Graphics receive pair 10- | PEG_RX10- | C86  | D86  | PEG_TX10- | PCIe Graphics transmit pair 10- |

| Power Ground                   | GND       | C87  | D87  | GND       | Power Ground                    |

| PCIe Graphics receive pair 11+ | PEG_RX11+ | C88  | D88  | PEG_TX11+ | PCIe Graphics transmit pair 11+ |

| PCle Graphics receive pair 11- | PEG_RX11- | C89  | D89  | PEG_TX11- | PCIe Graphics transmit pair 11- |

| Power Ground                   | GND       | C90  | D90  | GND       | Power Ground                    |

| PCle Graphics receive pair 12+ | PEG_RX12+ | C91  | D91  | PEG_TX12+ | PCIe Graphics transmit pair 12+ |

| PCle Graphics receive pair 12- | PEG_RX12- | C92  | D92  | PEG_TX12- | PCIe Graphics transmit pair 12- |

| Power Ground                   | GND       | C93  | D93  | GND       | Power Ground                    |

| PCIe Graphics receive pair 13+ | PEG_RX13+ | C94  | D94  | PEG_TX13+ | PCIe Graphics transmit pair 13+ |

| PCle Graphics receive pair 13- | PEG_RX13- | C95  | D95  | PEG_TX13- | PCIe Graphics transmit pair 13- |

| Power Ground                   | GND       | C96  | D96  | GND       | Power Ground                    |

| Not Connected                  | RSVD#C97  | C97  | D97  | RSVD#D97  | Not Connected                   |

| PCle Graphics receive pair 14+ | PEG_RX14+ | C98  | D98  | PEG_TX14+ | PCIe Graphics transmit pair 14+ |

| PCle Graphics receive pair 14- | PEG_RX14- | C99  | D99  | PEG_TX14- | PCIe Graphics transmit pair 14- |

| Power Ground                   | GND       | C100 | D100 | GND       | Power Ground                    |

| PCle Graphics receive pair 15+ | PEG_RX15+ | C101 | D101 | PEG_TX15+ | PCIe Graphics transmit pair 15+ |

| PCle Graphics receive pair 15- | PEG_RX15- | C102 | D102 | PEG_TX15- | PCIe Graphics transmit pair 15- |

| Power Ground                   | GND       | C103 | D103 | GND       | Power Ground                    |

| +12V switched power supply     | +12V_S    | C104 | D104 | +12V_S    | +12V switched power supply      |

| +12V switched power supply     | +12V_S    | C105 | D105 | +12V_S    | +12V switched power supply      |

| +12V switched power supply     | +12V_S    | C106 | D106 | +12V_S    | +12V switched power supply      |

| +12V switched power supply     | +12V_S    | C107 | D107 | +12V_S    | +12V switched power supply      |

| +12V switched power supply     | +12V_S    | C108 | D108 | +12V_S    | +12V switched power supply      |

| +12V switched power supply     | +12V_S    | C109 | D109 | +12V_S    | +12V switched power supply      |

| Power Ground                   | GND       | C110 | D110 | GND       | Power Ground                    |

|                                |           |      |      |           |                                 |

#### 3.3.2 PCI-e x4 Slots

CCOMe-C96

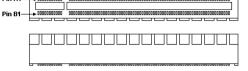

CCOMe-C96 board offer a possibility of expansion through two standard PCI-e x4 card edge connectors, type WINWIN p/n WPES-064AN41B22UWC or equivalent, with the pinout shown in the following table.

On first slot CN12, are carried out PCI-e lanes #0..#3 coming from COM Express<sup>™</sup> connector (rows A-B).

On second slot CN14, are carried out PCI-e lanes #4..#7 coming from COM Express<sup>™</sup> connector (rows A-B-C-D).

Please be aware that availability of all eight PCI express lanes depends on the COM Express<sup>™</sup> module used.

Please check the User Manual of the COM Express<sup>™</sup> module used for details about the availability of these lanes and all possible groupings that can be applied to these lanes.

On CCOMe-C96 carrier board, the PCI-express compatibility is ensured with devices up to Gen3.

| PCI-e x 4 Slot CN12                                                                                                                    |               |         |         |               |                                                                                                                                                                                    |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------|---------------|---------|---------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Description                                                                                                                            | Pin name      | Pin nr. | Pin nr. | Pin name      | Description                                                                                                                                                                        |  |  |  |

| +12V Power Rail                                                                                                                        | +12V_RUN      | B1      | A1      | PRSNT1#       | Hot Plug presence detect (tied to GND)                                                                                                                                             |  |  |  |

| +12V Power Rail                                                                                                                        | +12V_RUN      | B2      | A2      | +12V_RUN      | +12V Power Rail                                                                                                                                                                    |  |  |  |